# S12ZVC Evaluation Board Quick Start Guide

### **MagniV Mixed-signal MCUs**

by: Jesús Sánchez, Luis Olea

## 1 Introduction and default settings

This guide shows how to quickly connect the board to a host PC and execute a demonstration application preloaded in to the flash memory.

The S12ZVC MCU integrates:

- S12Z CPU

- · Power supply

- PNP external ballast transistor for VDDX, VDDA, and VDDC

- LED power indicators

- Reset

- LEDs

- Buzzer

- ADC potentiometer

- · Keyboard matrix

- · High-voltage input

- Sensors

- Temperature and humidity

- Pressure sensor

- Inertial sensor SPI X-Y axis

- SENT

- CAN

- LIN

Default jumper positions of the VLG-S12ZVC board are shown in the following section.

© 2014 Freescale Semiconductor, Inc.

### Contents

| 1 | Introduction and default settings          |

|---|--------------------------------------------|

| 2 | Device overview S12ZVC family              |

| 3 | Jumper default configuration               |

| 4 | Software tools installation                |

|   | 4.1 Install CodeWarrior development studio |

|   | 4.2 Launch the demo program                |

| 5 | Jumper list and description                |

| 6 | Headers and connectors list                |

| 7 | Peripheral list                            |

| 8 | References10                               |

| 9 | Revision history10                         |

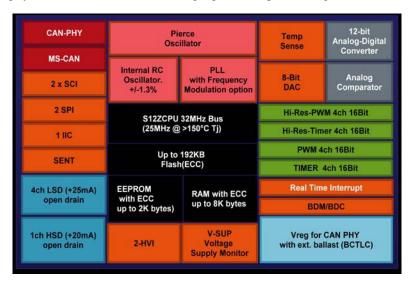

### 2 Device overview S12ZVC family

The MC9S12ZVC family is a new member of the S12 MagniV product line integrating a battery level (12 V) voltage regulator, supply voltage monitoring, high voltage inputs, and a CAN physical interface. It's primarily targeting at CAN nodes like sensors, switch panels, or small actuators. It offers various low-power modes and wake-up management to address state of the art power consumption requirements.

Some members of the MC9S12ZVC family are also offered for high temperature applications requiring AEC-Q100 Grade 0 (-40°C to +150°C ambient operating temperature range). The MC9S12ZVC family is based on the enhanced performance, linear address space S12Z core and delivers an optimized solution with the integration of several key system components into a single device, optimizing system architecture and achieving significant space savings.

Figure 1. S12ZVC architecture diagram1

### 3 Jumper default configuration

This section describes about the jumper configuration.

<sup>1.</sup> Block Diagram shows the maximum configuration. Not all pins or all peripherals are available on all devices and packages. Rerouting options are not shown.

# PRIMARY SIDE | PRIMA

Figure 2. Jumper configuration diagram

The following table lists the jumper default configuration.

Table 1. Jumper default configuration

| Header | Reference position                            |

|--------|-----------------------------------------------|

| J5     | 1-2                                           |

| J8     | 1-2                                           |

| J10    | 2-3                                           |

| J11    | 1-2                                           |

| J12    | 1-2                                           |

| J13    | 2-3                                           |

| J15    | 1-2                                           |

| J14    | 1-2                                           |

| J20    | 1-2, 3-4, 5-6, 7-8                            |

| J48    | 1,2                                           |

| J50    | 1-2, 3-4, 5-6, 7-8, 9-10, 11-12, 13-14, 15-16 |

| J16    | 1, 2                                          |

| J17    | 1, 2                                          |

| J18    | 1, 2                                          |

| J19    | 1, 2                                          |

| J22    | 1-2, 3-4, 5-6, 7-8                            |

| J25    | 1, 2                                          |

| J26    | 1- 2                                          |

### Software tools installation

Table 1. Jumper default configuration (continued)

| Header | Reference position |

|--------|--------------------|

| J29    | 1- 2               |

| J30    | 1-2                |

| J31    | 1-2                |

| J35    | 1-2                |

### 4 Software tools installation

This section describes how to get started with the S12ZVC board by installing CodeWarrior development studio and testing the demo program that comes programmed with the board.

### 4.1 Install CodeWarrior development studio

Freescale's CodeWarrior for MCUs integrates the development tools for several architectures, including the S12Z architecture, into a single product based on the Eclipse open development platform. Eclipse offers an excellent framework for building software development environments and is a standard framework used by many embedded software vendors.

The latest version of CodeWarrior for MCUs (Eclipse IDE) can be downloaded from **freescale.com/codewarrior**.

### 4.2 Launch the demo program

The S12ZVC EVB board comes preprogrammed with a small demonstration application that exercises the different modules of the S12ZVC MCU family, including the ADC, SCI, I2C, and GPIO modules.

To see this demonstration:

- 1. Connect a 12 V power source to the EVB.

- 2. Connect a USB cable to the USB type B connector.

- 3. Press the keys on the keypad to hear tones on the buzzer.

- 4. Tilt the EVB to observe changes on the red and green LEDs.

- 5. Rotate the potentiometer to observe changes on the orange LED.

- 6. Notice that the pressure sensor controls the yellow LED.

- 7. Set up a terminal program to the OSBDM CDC serial port. Set it to a 9600 baud rate and press any key; you will get a menu to read temperature and humidity from the I2C sensor.

The software for this application is available on **freescale.com**.

### 5 Jumper list and description

The following table lists all of the jumpers in the S12ZVC evaluation board and its corresponding configuration options.

Table 2. Jumpers description

| Jumper | Description                                                                                                                  |                                                                                                                                |  |

|--------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| J10    | HVI Circuit –Reference Voltage Selector                                                                                      |                                                                                                                                |  |

|        | Pin 1-2<br>Closed                                                                                                            | - SW1 is connected to VBAT level. This provides a HIGH voltage level when switch SW1 is pressed.                               |  |

|        | Pin 2-3<br>Closed                                                                                                            | - SW1 is connected to GND level. This provides a LOW voltage level when switch SW1 is pressed.                                 |  |

| J11    | HVI Circuit –Reference Voltage Selector                                                                                      |                                                                                                                                |  |

|        | Pin 1-2<br>Closed                                                                                                            | <ul> <li>SW2 is connected to VBAT level. This<br/>provides a HIGH voltage level when<br/>switch SW2 is pressed.</li> </ul>     |  |

|        | Pin 2-3<br>Closed                                                                                                            | <ul> <li>SW2 is connected to GND level. This<br/>provides a LOW voltage level when<br/>switch SW2 is pressed.</li> </ul>       |  |

| J12    | HVI Circuit –Reference Voltage Selector                                                                                      |                                                                                                                                |  |

|        | Pin 1-2<br>Closed                                                                                                            | <ul> <li>Enable VBAT level to pullup resistor.</li> <li>This provides a HIGH voltage level when switch SW2 is open.</li> </ul> |  |

|        | Pin 2-3<br>Closed                                                                                                            | Enable GND level to pullup resistor. This provides a LOW voltage level when switch SW2 is open.                                |  |

| J13    | HVI Circuit –Reference Voltage Selector                                                                                      |                                                                                                                                |  |

|        | Pin 1-2<br>Closed                                                                                                            | Enable VBAT level to pullup resistor.<br>This provides a HIGH voltage level when switch SW2 is open.                           |  |

|        | Pin 2-3<br>Closed                                                                                                            | Enable GND level to pullup resistor. This provide a LOW voltage level when switch SW2 is open.                                 |  |

| J14    | Buzzer Control                                                                                                               |                                                                                                                                |  |

|        | Closing this jumper enables the Buzzer of                                                                                    | control by PP7 port.                                                                                                           |  |

| J15    | Buzzer Power                                                                                                                 |                                                                                                                                |  |

|        | Closing this jumper powers the Buzzer circuit.                                                                               |                                                                                                                                |  |

| J16    | VDDX External Ballast Transistor                                                                                             |                                                                                                                                |  |

|        | With this jumper closed, the VSUP Voltage is connected to PNP external transistor collector for the VDDX voltage regulation. |                                                                                                                                |  |

| J17    | VDDX External Ballast Transistor                                                                                             |                                                                                                                                |  |

|        | This jumper enables the signal control of the PNP external transistor collector for the VDDX voltage regulation.             |                                                                                                                                |  |

| J18    | VDDC External Ballast Transistor                                                                                             |                                                                                                                                |  |

Table 2. Jumpers description (continued)

| Jumper | Description                                                                                                                  |                                                                                 |  |

|--------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|

|        | With this jumper closed, the VSUP Voltage is connected to PNP external transistor collector for the VDDC voltage regulation. |                                                                                 |  |

| J19    | VDDC External Ballast Transistor                                                                                             |                                                                                 |  |

|        | This jumper enables the signal control of the PNP external transistor collector for the VDDC voltage regulation.             |                                                                                 |  |

| J2     | Humidity and temperature sensor power                                                                                        | •                                                                               |  |

|        | Closing this jumper powers the humidity                                                                                      | and temperature sensor.                                                         |  |

| J20    | LEDs                                                                                                                         |                                                                                 |  |

|        | Pin 1-2                                                                                                                      | Red LED is connected to PP6 port                                                |  |

|        | Closed                                                                                                                       |                                                                                 |  |

|        | Pin 3-4                                                                                                                      | Green LED is connected to PP5 port                                              |  |

|        | Closed                                                                                                                       |                                                                                 |  |

|        | Pin 5-6                                                                                                                      | Yellow LED is connected to PP4 port                                             |  |

|        | Closed                                                                                                                       |                                                                                 |  |

|        | Pin 7-8                                                                                                                      | Orange LED is connected to PP0 port                                             |  |

|        | Closed                                                                                                                       |                                                                                 |  |

| J22    | Power Supply Voltages – LEDs Indicato                                                                                        | rs                                                                              |  |

|        | Pin 1-2                                                                                                                      | Enable VDDC - LED indicator                                                     |  |

|        | Closed                                                                                                                       |                                                                                 |  |

|        | Pin 3-4                                                                                                                      | Enable VDDA - LED indicator                                                     |  |

|        | Closed                                                                                                                       |                                                                                 |  |

|        | Pin 5-6                                                                                                                      | Enable VDDX - LED indicator                                                     |  |

|        | Closed                                                                                                                       |                                                                                 |  |

|        | Pin 7-8                                                                                                                      | Enable VSUP - LED indicator                                                     |  |

|        | Closed                                                                                                                       |                                                                                 |  |

| J25    | VDDC External Ballast Transistor - Outp                                                                                      | put                                                                             |  |

|        | Closing this jumper connects the externa VDDC_OUT line.                                                                      | al PNP ballast transistor output to                                             |  |

| J26    | VDDX External Ballast Transistor - Outp                                                                                      | ut                                                                              |  |

|        | Closing this jumper connects the externa VDD_OUT line.                                                                       | Closing this jumper connects the external PNP ballast transistor output to      |  |

| J29    | VDDA Power                                                                                                                   |                                                                                 |  |

|        | Closing this header connects VDDA to \                                                                                       | /DD_OUT line.                                                                   |  |

| J3     | Humidity Temperature Sensor - Commu                                                                                          | nication                                                                        |  |

|        | Closing this jumper connects the SCL-lin PT1.                                                                                | Closing this jumper connects the SCL-line of the Humidity Temperature Sensor to |  |

| J30    | VDDX                                                                                                                         |                                                                                 |  |

|        | Closing this jumper connects VDDX to V                                                                                       | Closing this jumper connects VDDX to VDD_OUT line.                              |  |

| J31    | VDDC                                                                                                                         |                                                                                 |  |

|        | Closing this jumper connects VDDC to VDDC_OUT line.                                                                          |                                                                                 |  |

Table 2. Jumpers description (continued)

| Jumper                     |                                                             | Description                                                                          |  |  |

|----------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| J32                        | SENT Transmitter Interface                                  | SENT Transmitter Interface                                                           |  |  |

|                            | Closing this header connect circuit.                        | Closing this header connects the SENT_TX line to SENT transmitter interface circuit. |  |  |

| J35                        | LIN Mode                                                    |                                                                                      |  |  |

|                            | With this jumper, the user ca<br>MC33662 - LIN transceiver. | an configure the local and remote wake-up mode of                                    |  |  |

| J38                        | LIN and SENT Communicat                                     | ion                                                                                  |  |  |

|                            | Pin 1-2                                                     | PS4 is connected to LIN_RX                                                           |  |  |

|                            | Closed                                                      |                                                                                      |  |  |

|                            | Pin 3-4                                                     | PS5 is connected to LIN_TX                                                           |  |  |

|                            | Closed                                                      |                                                                                      |  |  |

|                            | Pin 5-6                                                     | PS7 is connected to SENT_TX                                                          |  |  |

|                            | Closed                                                      |                                                                                      |  |  |

| J4                         | Humidity Temperature Sens                                   | or - Communication                                                                   |  |  |

|                            | Closing this jumper connects PT0.                           | Closing this jumper connects the SDA line of the humidity temperature sensor to      |  |  |

| J41                        | LIN – Master/Slave Mode                                     |                                                                                      |  |  |

|                            | With this jumper, the user ca                               | an configure as master or slave mode.                                                |  |  |

| J42                        | INERTIAL Sensor Power                                       |                                                                                      |  |  |

|                            | Closing this jumper powers                                  | the INERTIAL sensor circuit.                                                         |  |  |

| J44                        | CAN                                                         |                                                                                      |  |  |

|                            | Closing this jumper connects                                | s the SPLIT pin to the resistors termination of CAN.                                 |  |  |

| J47                        | Press Sensor Power                                          |                                                                                      |  |  |

|                            | Closing this jumper powers                                  | the press sensor circuit.                                                            |  |  |

| J48                        | Potentiometer Reference                                     |                                                                                      |  |  |

|                            | Closing this jumper connects                                | s the potentiometer to VDDA.                                                         |  |  |

| J5                         | VBAT                                                        |                                                                                      |  |  |

|                            | Closing this jumper connects                                | s VBAT to all system.                                                                |  |  |

| J50                        | Pin 1-2                                                     | Closing this jumper connects PAD8 port                                               |  |  |

|                            | Closed                                                      | to the potentiometer.                                                                |  |  |

|                            | Pin 3-4                                                     | Closing this jumper connects PAD9 port                                               |  |  |

|                            | Closed                                                      | to Press Sensor – Output.                                                            |  |  |

|                            | Pin 5-6                                                     | Closing this jumper connects PAD10                                                   |  |  |

|                            | Closed                                                      | port to the keyword matrix.                                                          |  |  |

|                            | Pin 7-8                                                     | Closing this jumper connects PAD11                                                   |  |  |

|                            | Closed                                                      | port to the keyword matrix.                                                          |  |  |

|                            | Pin 9-10                                                    | Closing this jumper connects PAD12                                                   |  |  |

|                            | Closed                                                      | port to the keyword matrix.                                                          |  |  |

| Pin 11-12 Closing this jur |                                                             | Closing this jumper connects PAD13                                                   |  |  |

|                            |                                                             | port to the keyword matrix.                                                          |  |  |

Table 2. Jumpers description (continued)

| Jumper | Description                                                                                                                |                                                                |  |

|--------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

|        | Pin 13-14                                                                                                                  | Closing this jumper connects PAD14 port to the keyword matrix. |  |

|        | Closed                                                                                                                     |                                                                |  |

|        | Pin 15-16 Closing this jumper conn                                                                                         |                                                                |  |

|        | Closed                                                                                                                     | port to the keyword matrix.                                    |  |

| J51    | VDDX shunt resistor                                                                                                        |                                                                |  |

|        | Closing this jumper enables a shunt resistor on VDDX that can aid on current measurements for the VDDX ballast transistor. |                                                                |  |

| J52    | VDDC shunt resistor                                                                                                        |                                                                |  |

|        | Closing this jumper enables a shunt resistor on VDDC that can aid on current measurements for the VDDC ballast transistor. |                                                                |  |

| J8     | LEDs Power                                                                                                                 |                                                                |  |

|        | Closing this jumper connects VDDX to D4, D6, D13, and D15.                                                                 |                                                                |  |

### 6 Headers and connectors list

The following table lists all of the connectors available in the S12ZVC evaluation board and their corresponding signals.

**Table 3. Connectors description**

| Header / Connector | Description                                                                                                                                                                              |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| J1                 | Main power connector (up to 18 V)                                                                                                                                                        |  |

| J21                | VBAT, VSUP, VDDX, VDDC, and VDDA are connected to this header.                                                                                                                           |  |

| J23                | HVI Header – External HVI signal                                                                                                                                                         |  |

|                    | This jumper allows a monitoring/measurement of the High voltage signal. If J13 and J10 are disabled, the user can apply an external signal. This jumper (pin 1-2) should always be OPEN. |  |

| J24                | HVI Header – External HVI signal                                                                                                                                                         |  |

|                    | This jumper allows a monitoring/measurement of the High voltage signal. If J11 and J12 are disabled, the user can apply an external signal. This jumper (pin 1-2) should always be OPEN. |  |

| J27                | GPIO Header - Port T                                                                                                                                                                     |  |

| J28                | SENT transmitter header with GND                                                                                                                                                         |  |

| J33                | GPIO Header - Port P                                                                                                                                                                     |  |

| J34                | BDM Connector                                                                                                                                                                            |  |

| J37                | LIN Connector                                                                                                                                                                            |  |

| J39                | GPIO Header - Port AD                                                                                                                                                                    |  |

| J40                | GPIO Header - Port S                                                                                                                                                                     |  |

| J45                | CAN main connector                                                                                                                                                                       |  |

Table 3. Connectors description (continued)

| Header / Connector | Description                                                                                                                                                                                                                       |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J46                | CAN main connector                                                                                                                                                                                                                |

| J49                | OSBDM USB port for programming and debugging the main MCU.                                                                                                                                                                        |

| J6                 | VDDX - PNP Ballast Transistor Terminals                                                                                                                                                                                           |

|                    | The header could be used for measurements/monitoring of all signals of the external PNP ballast transistor: Base, Collector, and Emitter. Opening J16, J17, and J27 connects the user to an additional transistor for validation. |

| J7                 | VDDC – PNP Ballast Transistor Terminals                                                                                                                                                                                           |

|                    | The header could be used for measurements/monitoring of all signals of the external PNP ballast transistor: Base, Collector, and Emitter. Opening J18, J19, and J25 connects the user to an additional transistor for validation. |

| J9                 | Main power connector (up to 18 V)                                                                                                                                                                                                 |

### 7 Peripheral list

The following table lists all the peripherals available in the S12ZVC evaluation board.

Table 4. Peripheral description

| Peripheral              | ID   | MCU PORT | Description                                          |

|-------------------------|------|----------|------------------------------------------------------|

| Potentiometer           | R76  | PAD8     | Potentiometer connected to ADC channel 8             |

| LED – Voltage Indicator | D7   | -        | VSUP LED indicator                                   |

|                         | D10  | -        | VDDX LED indicator                                   |

|                         | D14  | -        | VDDA LED indicator                                   |

|                         | D16  | -        | VDDC LED indicator                                   |

| Switch Panel            | SW4  | -        | Matrix keyboard switch                               |

|                         | SW5  | -        |                                                      |

|                         | SW6  | -        |                                                      |

|                         | SW7  | -        |                                                      |

|                         | SW8  | -        |                                                      |

|                         | SW9  | -        |                                                      |

|                         | SW10 | -        |                                                      |

|                         | SW11 | -        |                                                      |

|                         | SW12 | -        |                                                      |

| High Voltage Switch     | SW1  | PL1      | Switch connected to PL1 (with 10 $k\Omega$ resistor) |

|                         | SW2  | PL0      | Switch connected to PL0 (with 10 $k\Omega$ resistor) |

### References

Table 4. Peripheral description (continued)

| Peripheral            | ID  | MCU PORT | Description                      |

|-----------------------|-----|----------|----------------------------------|

| Buzzer                | LS1 | PP7      | Buzzer controlled by PP7         |

| LED – General purpose | D4  | PP6      | Red LED connected to port PP6    |

|                       | D6  | PP5      | Green LED connected to port PP5  |

|                       | D13 | PP4      | Yellow LED connected to port PP4 |

|                       | D15 | PP0      | Orange LED connected to port PP0 |

| Reset                 | SW3 | -        | Reset switch                     |

### 8 References

For further reference, the following documents are available at **freescale.com**.

- 1. AN4851: Using the High Resolution Timer and PWM in the S12ZVC (AN4851)

- 2. AN4852: Using the SENT Transmitter Module in S12ZVC Devices (AN4852)

### 9 Revision history

| Revision number | Date    | Substantial changes |

|-----------------|---------|---------------------|

| 0               | 01/2014 | Initial release     |

### How to Reach Us:

**Home Page:**

freescale.com

Web Support:

freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/

Freescale, the Freescale logo, AltiVec, C-5, CodeTest, CodeWarrior, ColdFire, ColdFire+, C-Ware, Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, QorlQ, Qorivva, StarCore, Symphony, and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, CoreNet, Flexis, Layerscape, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SafeAssure, SafeAssure logo, SMARTMOS, Tower, TurboLink, Vybrid, and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© 2014 Freescale Semiconductor, Inc.

Document Number S12ZVCEBQSG Revision 0, 01/2014