#### **Features:**

- V<sub>DS</sub>, 40V

- R<sub>DS(on)</sub>, 325 mΩ

- I<sub>D</sub>, 2.7 A

- Optimized eGaN® FET for high frequency applications

- Pb-Free (RoHS Compliant), Halogen Free

### **Applications:**

- Ultra high speed DC-DC conversion

- RF Envelope Tracking

- Wireless Power Transfer

- Game console and industrial movement sensing (LiDAR)

EPC8008 eGaN FETs are supplied only in passivated die form with solder bars

#### **MAXIMUM RATINGS**

| Parameter                                                        | Value                            |

|------------------------------------------------------------------|----------------------------------|

| Maximum Drain – Source Voltage                                   | 40 V                             |

| Gate – Source Maximum Voltage Range                              | -5 V < V <sub>GS</sub> < 6 V     |

| Continuous Drain Current, 25 °C, θ <sub>JA</sub> = 33            | 2.7 A                            |

| Maximum Pulsed Drain Current, 25 °C, T <sub>pulse</sub> = 300 μs | 2.9 A                            |

| Operating Temperature Range                                      | -40 °C < T <sub>J</sub> < 150 °C |

#### **STATIC CHARACTERISTICS**

| Parameter                              | Conditions                                    | Value                                                      |

|----------------------------------------|-----------------------------------------------|------------------------------------------------------------|

| Maximum Drain – Source Leakage         | V <sub>DS</sub> = 32 V, V <sub>GS</sub> = 0 V | 0.1 mA                                                     |

| Maximum R <sub>DS(ON)</sub>            | $V_{GS} = 5 \text{ V}, I_D = 0.5 \text{ A}$   | 325 mΩ                                                     |

| Gate – Source Threshold Voltage        | $V_{DS} = V_{GS}, I_{D} = 0.25 \text{ mA}$    | $0.7 \text{ V} < \text{V}_{\text{GS(TH)}} < 2.5 \text{ V}$ |

| Gate – Source Maximum Positive Leakage | V <sub>GS</sub> = 5 V                         | 0.5 mA                                                     |

| Gate – Source Maximum Negative Leakage | V <sub>GS</sub> = -5 V                        | -0.1 mA                                                    |

$T_J = 25$  °C unless otherwise stated

Specifications are with Substrate shorted to Source where applicable

### **DYNAMIC CHARACTERISTICS**

| Parameter                                       | Conditions                                    | Typical Value |

|-------------------------------------------------|-----------------------------------------------|---------------|

| C <sub>ISS</sub> (Input Capacitance)            |                                               | 25 pF         |

| C <sub>OSS</sub> (Output Capacitance)           | V <sub>DS</sub> = 20 V; V <sub>GS</sub> = 0 V | 8 pF          |

| C <sub>RSS</sub> (Reverse Transfer Capacitance) |                                               | 0.2 pF        |

| Q <sub>G</sub> (Total Gate Charge)              |                                               | 177 pC        |

| Q <sub>GD</sub> (Gate to Drain Charge)          | V <sub>DS</sub> = 20 V; I <sub>D</sub> = 1 A  | 12 pC         |

| Q <sub>GS</sub> (Gate to Source Charge)         |                                               | 67 pC         |

| Q <sub>OSS</sub> (Output Charge)                | V <sub>DS</sub> = 20 V; V <sub>GS</sub> = 0 V | 211 pC        |

| Q <sub>RR</sub> (Source-Drain Recovery Charge)  |                                               | 0 pC          |

$T_J = 25$  °C unless otherwise stated

Specifications are with Substrate shorted to Source where applicable

### THERMAL CHARACTERISTICS

|                  |                                                  | TYP |      |

|------------------|--------------------------------------------------|-----|------|

| R <sub>eJC</sub> | Thermal Resistance, Junction to Case             | 6.7 | °C/W |

| R <sub>eJB</sub> | Thermal Resistance, Junction to Board            | 33  | °C/W |

| R <sub>eJA</sub> | Thermal Resistance, Junction to Ambient (Note 1) | 82  | °C/W |

Note 1: R<sub>0JA</sub> is determined with the device mounted on one square inch of copper pad, single layer 2 oz copper on FR4 board. See <a href="http://epc-co.com/epc/documents/product-training/Appnote Thermal Performance of eGan FETs.pdf">http://epc-co.com/epc/documents/product-training/Appnote Thermal Performance of eGan FETs.pdf</a> for details.

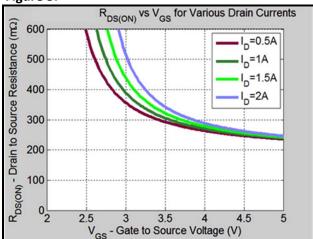

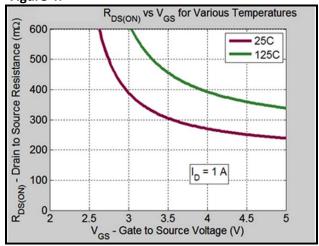

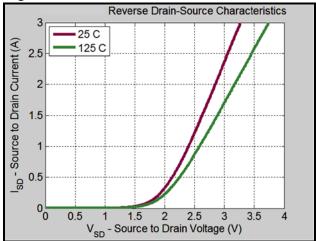

Figure 3:

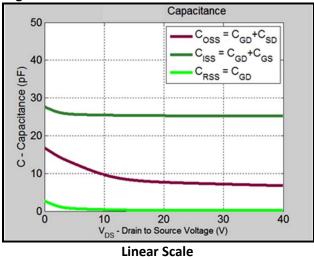

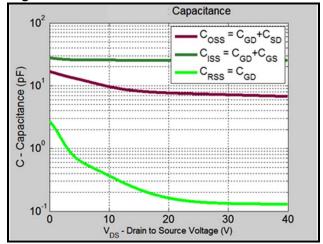

Figure 5a:

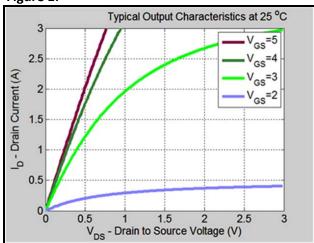

Figure 2:

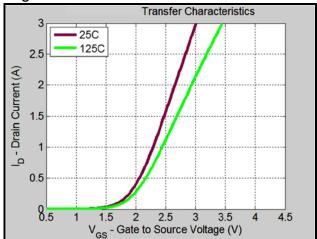

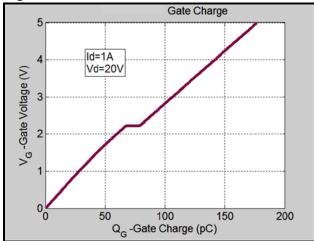

Figure 4:

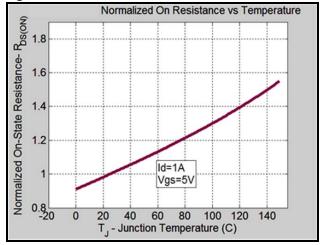

Figure 5b:

Log Scale

Figure 8:

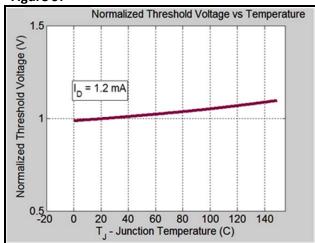

All measurements were done with substrate shorted to source

Figure 7:

Figure 9:

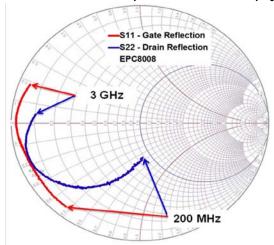

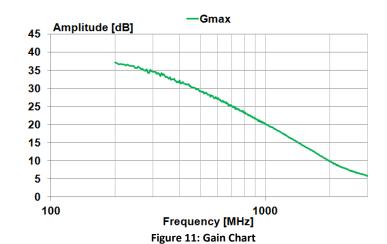

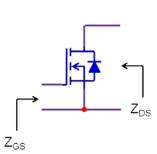

#### S-PARAMETER CHARACTERISTICS

$V_{GSQ}$  = 1.36 V,  $V_{DSQ}$  = 20 V,  $I_{DQ}$  = 0.20 A Pulsed measurement, Heat-Sink Installed,  $Z_0$  = 50  $\Omega$

Figure 10: Smith Chart

**Frequency** Gate (Z<sub>GS</sub>) Drain (Z<sub>DS</sub>) [MHz]  $[\Omega]$  $[\Omega]$ 200 2.85 - j23.6243.87 - j27.69 500 2.15 - j9.2718.81 - j28.701000 1.25 - j3.135.58 - j16.481200 1.10 - j1.663.68 - j13.311500 0.91 + j0.272.48 - j9.042000 1.09 + j3.202.71 - j3.842400 1.35 + j5.393.67 - j0.93 3000 2.19 + j9.375.10 + j2.36

Table 1: S-Parameter Table

Download S-parameter files at www.epc-co.com

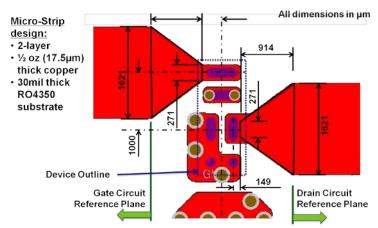

Figure 12: Device Reflection

Figure 13: Taper and Reference Plane details - Device Connection

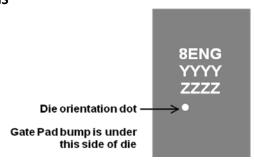

### **DIE MARKINGS**

|             | Laser Marking  |                |                |

|-------------|----------------|----------------|----------------|

| Part Number | Part #         | Lot_Date Code  | Lot_Date Code  |

|             | Marking Line 1 | Marking Line 2 | Marking Line 3 |

| EPC8008     | 8ENG           | YYYY           | ZZZZ           |

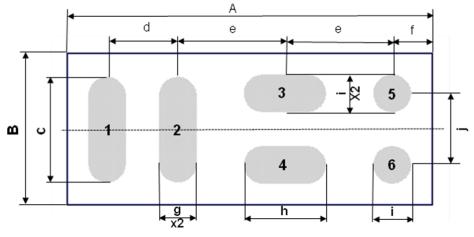

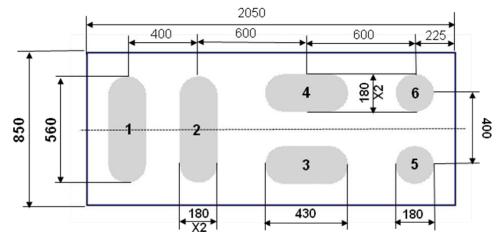

### DIE OUTLINE Solder Bar View

| DIM | MICROMETERS |         |      |

|-----|-------------|---------|------|

| DIM | MIN         | Nominal | MAX  |

| А   | 2020        | 2050    | 2080 |

| В   | 820         | 850     | 880  |

| С   | 555         | 580     | 605  |

| d   | 400         | 400     | 400  |

| e   | 600         | 600     | 600  |

| f   | 200         | 225     | 250  |

| g   | 175         | 200     | 225  |

| h   | 425         | 450     | 475  |

| i   | 175         | 200     | 225  |

| j   | 400         | 400     | 400  |

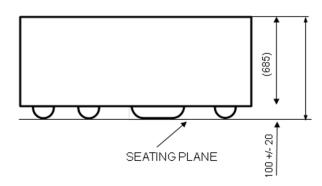

### **Side View**

### **RECOMMENDED LAND PATTERN**

(units in  $\mu$ m)

Pad no. 1 is Gate

Pad no. 2 is Source Return for Gate Driver

Pad no. 3 and 5 are Source

Pad no. 4 is Drain

Pad no. 6 is Substrate

Land pattern is solder mask defined Solder mask opening is 10 µm smaller per side than bump

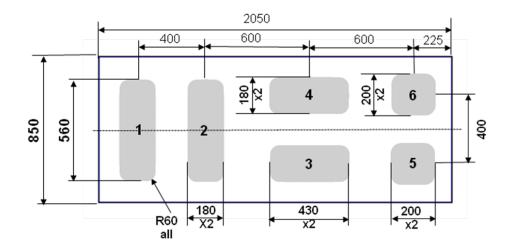

#### **RECOMMENDED STENCIL**

(units in  $\mu$ m)

Pad no. 1 is Gate

Pad no. 2 is Source Return for Gate Driver

Pad no. 3 and 5 are Source

Pad no. 4 is Drain

Pad no. 6 is Substrate

Recommended stencil should be 4mil (100 $\mu$ m) thick, must be laser cut, openings per drawing. Note that openings for pads 5 & 6 are larger than solder mask opening.

Efficient Power Conversion Corporation (EPC) reserves the right to make changes without further notice to any products herein. Preliminary specification sheet contains information regarding a product EPC is considering for production release. EPC does not assume any liability arising out of the application or use of any product or circuit described herin; neither does it convey any license under its patent rights, nor the rights of other.

$\mathsf{eGAN}^*$  is a registered trademark of Efficient Power Conversion Corporation. U.S. Patents 8,350,294; 8,404,508; 8,431,960; 8,436,398

Revised September, 2013