**CMOSIC**

# 1/1 to 1/4 Duty General-Purpose LCD Display Driver with LED Driver

http://onsemi.com

#### Overview

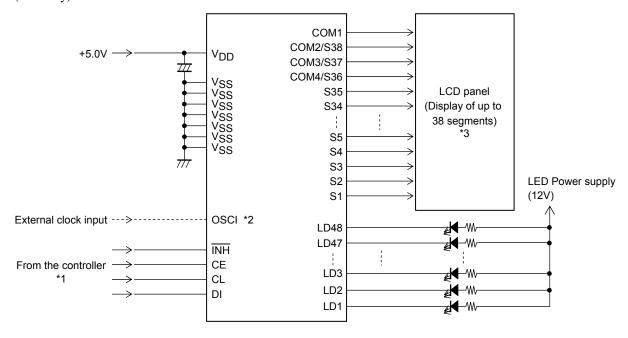

LC75805PE is the 1/1 to 1/4 duty general-purpose LCD display driver with the LED driver to use for the instrument panel display by control with the controller. In addition, LC75805PE is able to drive up to 48 LED and LCD of up to 140 segments directly, and has a built-in 7ch PWM function for brightness adjustment of LED. Furthermore, because of built-in the oscillator circuit, it is possible to reduce external resister and capacitor for oscillation.

#### **Features**

• Switch of Static Drive, 1/2 Duty Drive, 1/3 Duty Drive and 1/4 Duty Drive can be controlled by serial data.

Static Drive (1/1 Duty Drive) : Capable of driving up to 38 segments.

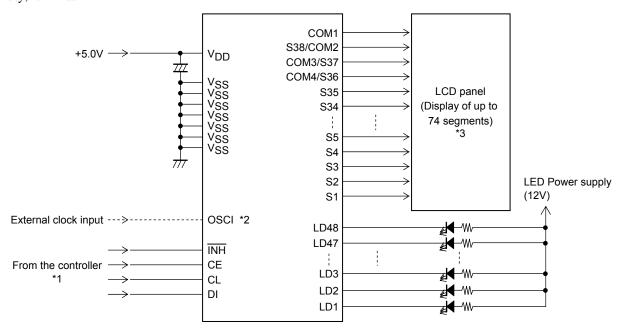

1/2 Duty Drive : Capable of driving up to 74 segments.

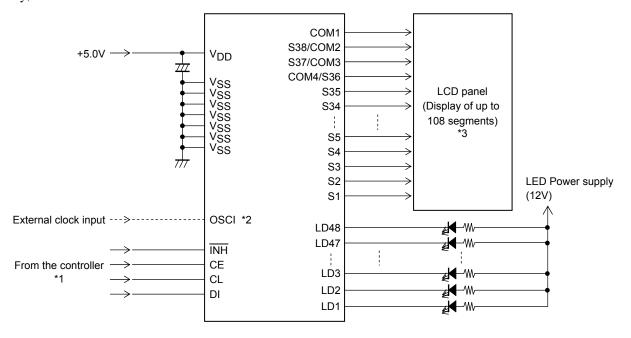

1/3 Duty Drive : Capable of driving up to 108 segments.

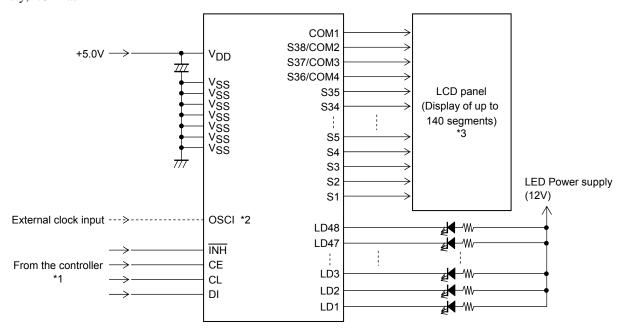

1/4 Duty Drive : Capable of driving up to 140 segments.

- Frame frequency of common and segment output waveform can be controlled by serial data.

- Turning on/off LED can be controlled by serial data. (Capable of driving up to 48 LED)

- Built-in 7ch PWM function for brightness adjustment of LED. (Resolution of 128 steps)

- Frame frequency of LED driver output waveform can be controlled by serial data.

- Serial data input supports CCB format communication with the system controller. (Support 5V operation)

- Backup function and forced turning off all segments by power-saving mode can be controlled by serial data.

- Switch of the internal oscillator operating mode and the external clock operating mode can be controlled by serial data.

- High generality, since display data is displayed directly without the intervention of a decoder circuit.

- The INH pin allows the display to be forced to the off state.

- Built-in Oscillator circuit (Built-in resister and capacitor for oscillation)

- CCB is ON Semiconductor® 's original format. All addresses are managed by ON Semiconductor® for this format.

QIP100E(14X20)

• CCB is a registered trademark of Semiconductor Components Industries, LLC.

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 34 of this data sheet.

# **Specifications**

# Absolute Maximum Ratings at Ta = 25°C, $V_{SS} = 0V$

| Parameter                   | Symbol              | Conditions              | Ratings                      | Unit |

|-----------------------------|---------------------|-------------------------|------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max | V <sub>DD</sub>         | -0.3 to +6.5                 | V    |

| Input voltage               | V <sub>IN</sub> 1   | CE, CL, DI, INH, OSCI   | -0.3 to +6.5                 | ٧    |

| Output voltage              | V <sub>OUT</sub> 1  | S1 to S38, COM1 to COM4 | -0.3 to V <sub>DD</sub> +0.3 | .,   |

|                             | V <sub>OUT</sub> 2  | LD1 to LD48             | -0.3 to +35                  | V    |

| Output current              | I <sub>OUT</sub> 1  | S1 to S38               | 300                          | μА   |

|                             | I <sub>OUT</sub> 2  | COM1 to COM4            | 3                            | 4    |

|                             | I <sub>OUT</sub> 3  | LD1 to LD48             | 30                           | mA   |

| Allowable power dissipation | Pd max              | Ta=95°C                 | 400                          | mW   |

| Operating temperature       | Topr                |                         | -40 to +95                   | °C   |

| Storage temperature         | Tstg                |                         | -55 to +150                  | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# Allowable Operating Ranges at $Ta = -40 \text{ to } +95^{\circ}\text{C}, V_{SS} = 0\text{V}$

| D l                                | 0                 | 0                                           | Ratings            |     |                    | 11.2     |

|------------------------------------|-------------------|---------------------------------------------|--------------------|-----|--------------------|----------|

| Parameter                          | Symbol            | nbol Conditions                             | min                | typ | max                | Unit     |

| Supply voltage                     | $V_{DD}$          | $V_{DD}$                                    | 4.5                |     | 5.5                | ٧        |

| Input high-level voltage           | V <sub>IH</sub> 1 | CE, CL, DI, INH                             | 0.8V <sub>DD</sub> |     | 5.5                | V        |

|                                    | V <sub>IH</sub> 2 | OSCI                                        | 0.8V <sub>DD</sub> |     | 5.5                | ٧        |

| Input low-level voltage            | V <sub>IL</sub> 1 | CE, CL, DI, INH                             | 0                  |     | 0.2V <sub>DD</sub> | V        |

|                                    | V <sub>IL</sub> 2 | OSCI                                        | 0                  |     | 0.2V <sub>DD</sub> | V        |

| Output pull-up voltage             | V <sub>OUP</sub>  | LD1 to LD48, V <sub>DD</sub> = 4.5 to 5.5V  | 0                  |     | 30                 | <b>V</b> |

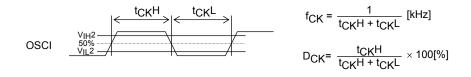

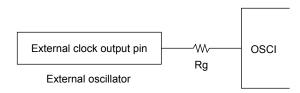

| External clock operating frequency | fCK               | OSCI, External clock operating mode [Fig 3] | 100                | 300 | 600                | kHz      |

| External clock duty                | D <sub>CK</sub>   | OSCI, External clock operating mode [Fig 3] | 30                 | 50  | 70                 | %        |

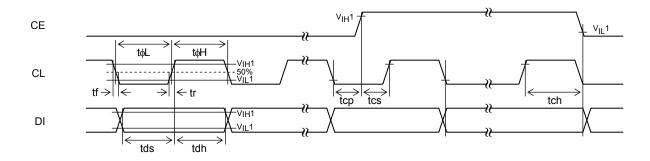

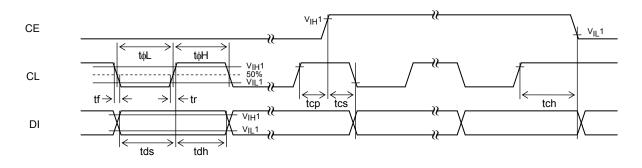

| Data setup time                    | tds               | CL, DI [Fig 1], [Fig 2]                     | 160                |     |                    | ns       |

| Data hold time                     | tdh               | CL, DI [Fig 1], [Fig 2]                     | 160                |     |                    | ns       |

| CE wait time                       | tcp               | CE, CL [Fig 1], [Fig 2]                     | 160                |     |                    | ns       |

| CE setup time                      | tcs               | CE, CL [Fig 1], [Fig 2]                     | 160                |     |                    | ns       |

| CE hold time                       | tch               | CE, CL [Fig 1], [Fig 2]                     | 160                |     |                    | ns       |

| High-level clock pulse width       | tφH               | CL [Fig 1], [Fig 2]                         | 160                |     |                    | ns       |

| Low-level clock pulse width        | tφL               | CL [Fig 1], [Fig 2]                         | 160                |     |                    | ns       |

| Rise time                          | tr                | CE, CL, DI [Fig 1], [Fig 2]                 |                    | 160 |                    | ns       |

| Fall time                          | tf                | CE, CL, DI [Fig 1], [Fig 2]                 |                    | 160 |                    | ns       |

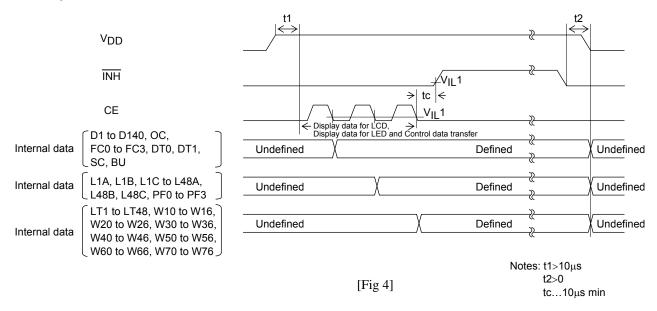

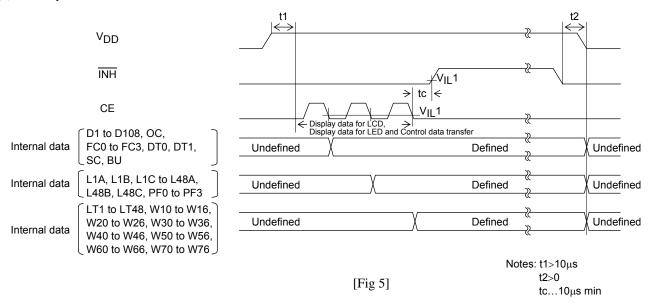

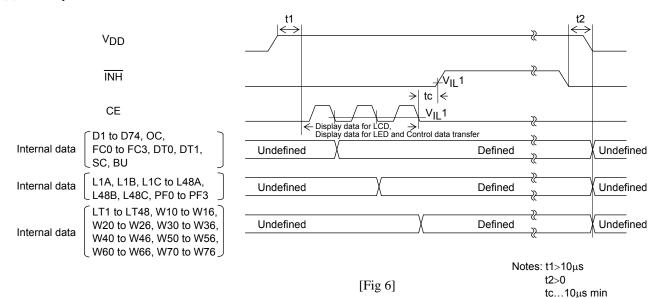

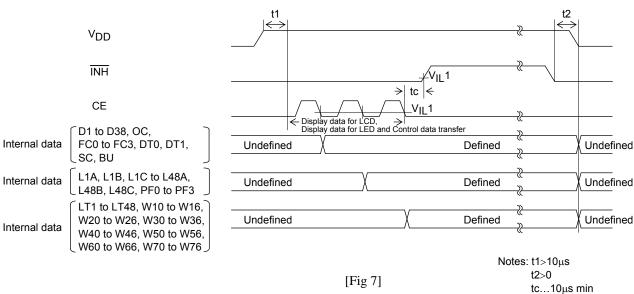

| INH switching time                 | tc                | NH, CE [Fig 4], [Fig 5], [Fig 6], [Fig 7]   | 10                 |     |                    | μS       |

# **Electrical Characteristics** for the Allowable Operating Ranges

| Darameter                   | Symbol             | Pin                | Conditions                                                                                                                                                                              |                            | Unit               |                            |      |

|-----------------------------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------|----------------------------|------|

| Parameter                   | Symbol             | PIII               |                                                                                                                                                                                         | min                        | typ                | max                        | Unit |

| Hysteresis                  | V <sub>H</sub>     | CE, CL, DI, INH    |                                                                                                                                                                                         |                            | 0.1V <sub>DD</sub> |                            | V    |

| Input high-level current    | I <sub>IH</sub> 1  | CE, CL, DI, INH    | V <sub>I</sub> = 5.5V                                                                                                                                                                   |                            |                    | 5.0                        | •    |

|                             | I <sub>IH</sub> 2  | OSCI               | V <sub>I</sub> = 5.5V                                                                                                                                                                   |                            |                    | 5.0                        | μА   |

| Input low-level current     | I <sub>IL</sub> 1  | CE, CL, DI, INH    | V <sub>I</sub> = 0V                                                                                                                                                                     | -5.0                       |                    |                            |      |

|                             | I <sub>IL</sub> 2  | OSCI               | V <sub>1</sub> = 0V                                                                                                                                                                     | -5.0                       |                    |                            | μА   |

| Output OFF leak current     | loffh              | LD1 to LD48        | V <sub>O</sub> = 30V                                                                                                                                                                    |                            |                    | 5.0                        | μΑ   |

| Output high-level voltage   | V <sub>OH</sub> 1  | S1 to S38          | I <sub>O</sub> = -20μA                                                                                                                                                                  | V <sub>DD</sub> -0.9       |                    |                            | .,   |

|                             | V <sub>OH</sub> 2  | COM1 to COM4       | I <sub>O</sub> = -100μA                                                                                                                                                                 | V <sub>DD</sub> -0.9       |                    |                            | V    |

| Output low-level voltage    | V <sub>OL</sub> 1  | S1 to S38          | I <sub>O</sub> = 20μA                                                                                                                                                                   |                            |                    | 0.9                        |      |

|                             | V <sub>OL</sub> 2  | COM1 to COM4       | I <sub>O</sub> = 100μA                                                                                                                                                                  |                            |                    | 0.9                        | V    |

|                             | V <sub>OL</sub> 3  | LD1 to LD48        | I <sub>O</sub> = 20mA                                                                                                                                                                   |                            | 0.25               | 0.5                        |      |

| Output middle-level voltage | V <sub>MID</sub> 1 | S1 to S36          | 1/3 bias I $_{ m O}$ = ±20 $\mu$ A                                                                                                                                                      | 2/3V <sub>DD</sub><br>-0.9 |                    | 2/3V <sub>DD</sub><br>+0.9 |      |

|                             | V <sub>MID</sub> 2 | S1 to S36          | 1/3 bias I <sub>O</sub> = ±20μA                                                                                                                                                         | 1/3V <sub>DD</sub><br>-0.9 |                    | 1/3V <sub>DD</sub><br>+0.9 |      |

|                             | V <sub>MID</sub> 3 | COM1 to COM4       | 1/3 bias I <sub>O</sub> = ±100μA                                                                                                                                                        | 2/3V <sub>DD</sub><br>-0.9 |                    | 2/3V <sub>DD</sub><br>+0.9 | ٧    |

|                             | V <sub>MID</sub> 4 | COM1 to COM4       | 1/3 bias I <sub>O</sub> = ±100μA                                                                                                                                                        | 1/3V <sub>DD</sub><br>-0.9 |                    | 1/3V <sub>DD</sub><br>+0.9 |      |

|                             | V <sub>MID</sub> 5 | COM1, COM2         | 1/2 bias I <sub>O</sub> = ±100μA                                                                                                                                                        | 1/2V <sub>DD</sub><br>-0.9 |                    | 1/2V <sub>DD</sub><br>+0.9 |      |

| Oscillator frequency        | fosc               | Oscillator circuit | Internal oscillator operating mode                                                                                                                                                      | 240                        | 300                | 360                        | kHz  |

| Current drain               | I <sub>DD</sub> 1  | $V_{DD}$           | Power save mode                                                                                                                                                                         |                            |                    | 15                         |      |

|                             | I <sub>DD</sub> 2  | V <sub>DD</sub>    | V <sub>DD</sub> = 5.5V Output open, Internal oscillator operating mode                                                                                                                  |                            | 750                | 1500                       |      |

|                             | I <sub>DD</sub> 3  | V <sub>DD</sub>    | V <sub>DD</sub> = 5.5V<br>Output open,<br>External clock operating mode<br>f <sub>CK</sub> = 300kHz<br>V <sub>IH</sub> 2 = 0.9V <sub>DD</sub><br>V <sub>IL</sub> 2 = 0.1V <sub>DD</sub> |                            | 750                | 1500                       | μА   |

<sup>\*</sup> Electrical Characteristics might be changed for the improvement without notice.

# 1. When CL is stopped at the low level.

[Fig 1]

# 2. When CL is stopped at the high level.

[Fig 2]

# 3. OSCI pin clock timing in external clock operating mode.

[Fig 3]

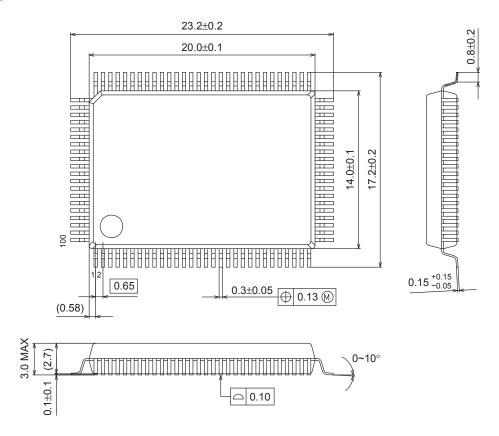

# **Package Dimensions**

unit: mm

#### PQFP100 14x20 / QIP100E

CASE 122BV ISSUE A

#### **SOLDERING FOOTPRINT\***

NOTE: The measurements are not to guarantee but for reference only.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code Y = Year M = Month DDD = Additional Traceability Data

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot "■", may or may not be present.

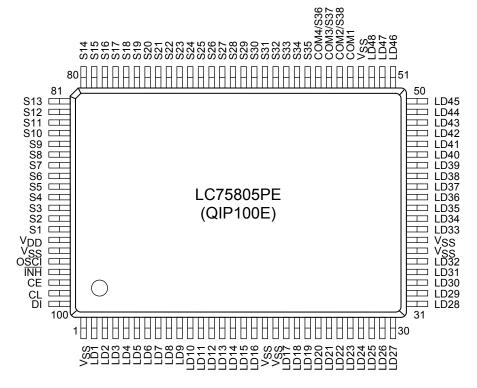

# **Pin Assignment**

Top view

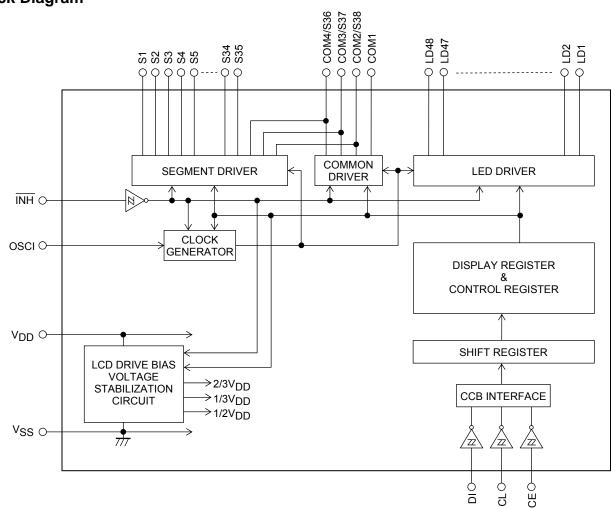

# **Block Diagram**

# **Pin Functions**

| Symbol                                      | Pin No.                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Active | I/O | Handling<br>when<br>unused |

|---------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|----------------------------|

| LD1 to LD16<br>LD17 to LD32<br>LD33 to LD48 | 2 to 17<br>20 to 35<br>38 to 53       | These are LED driver output pins that display the display data for LED transferred by serial data input, and high- voltage open-drain output pins. (Pull-up voltage is 30[V] maximum.) In addition, brightness adjustment of LED is possible by PWM function, too.                                                                                                                                                                                                                                                       | -      | 0   | OPEN                       |

| COM1<br>COM2/S38<br>COM3/S37<br>COM4/S36    | 55<br>56<br>57<br>58                  | These are common driver output pins, and Frame frequency is fo [Hz]. COM2/S38, COM3/S37 and COM4/S36 are possible to be used as the segment output by control data.                                                                                                                                                                                                                                                                                                                                                      | -      | 0   | OPEN                       |

| S35 to S1                                   | 59 to 93                              | These are segment output pins that display the display data for LCD transferred by serial data input.                                                                                                                                                                                                                                                                                                                                                                                                                    | -      | 0   | OPEN                       |

| OSCI                                        | 96                                    | This is input pin for the external clock.  Input the clock whose frequency (f <sub>CK</sub> ) is between 100 and 600[kHz] at external clock operating mode.  Furthermore, connect to GND at internal oscillator operating mode.                                                                                                                                                                                                                                                                                          | -      | 1   | GND                        |

| CE                                          | 98                                    | These are input pins for serial data transfer, and connect to the controller.                                                                                                                                                                                                                                                                                                                                                                                                                                            | Н      | I   |                            |

| CL                                          | 99                                    | CE: Chip enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | ı   | GND                        |

| DI                                          | 100                                   | CL: Synchronized clock DI: Transfer data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _      | 1   |                            |

| ĪNH                                         | 97                                    | Display off control input pin  • INH = Low-level (VSS)Display forced off  LD1 to LD48 = Z (High-impedance)  COM1 = L (VSS)  COM2/S38 to COM4/S36 = L (VSS)  S1 to S35 = L (VSS)  Internal oscillator operation is stopped.  External clock input is forbidden.  • INH = High-level (VDD)Display on  Internal oscillator operation is possible.  (At Internal oscillator operating mode)  External clock input is possible.  (At External clock operating mode)  However, serial data can be transferred during turn off. | L      | ı   | GND                        |

| V <sub>DD</sub>                             | 94                                    | This is power supply pin. Supply the voltage between 4.5V and 5.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -      | -   | -                          |

| V <sub>SS</sub>                             | 1<br>18<br>19<br>36<br>37<br>54<br>95 | These are power supply pins. Connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -      | -   | -                          |

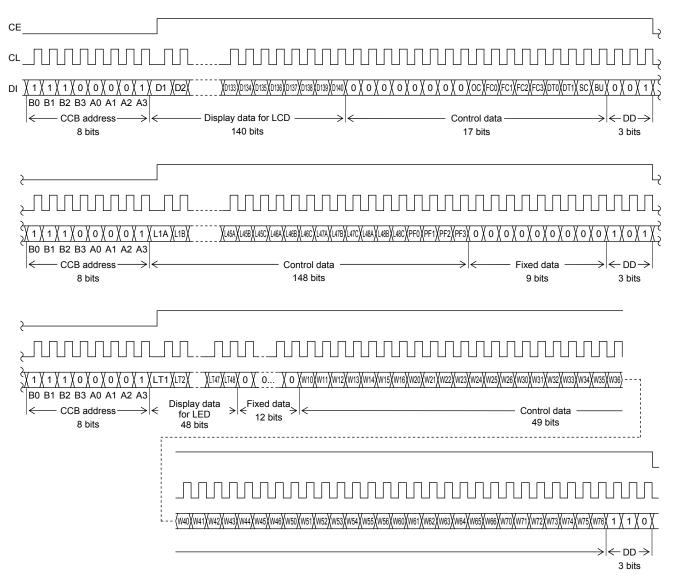

#### **Serial Data Transfer Format**

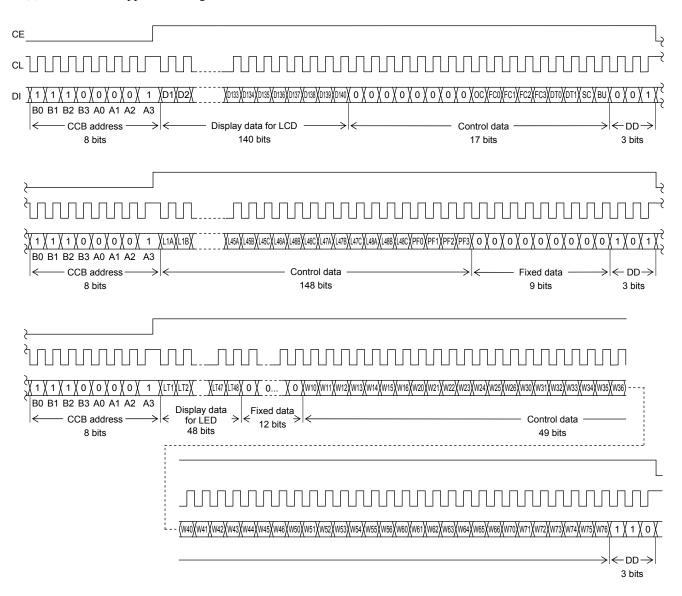

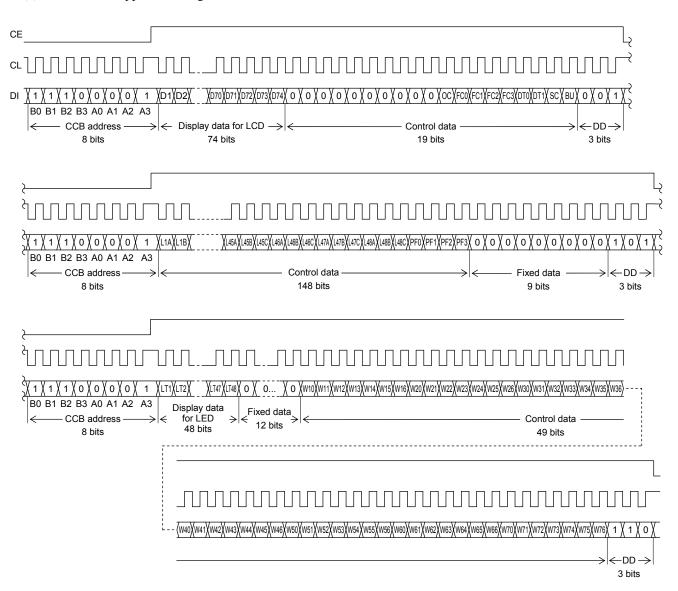

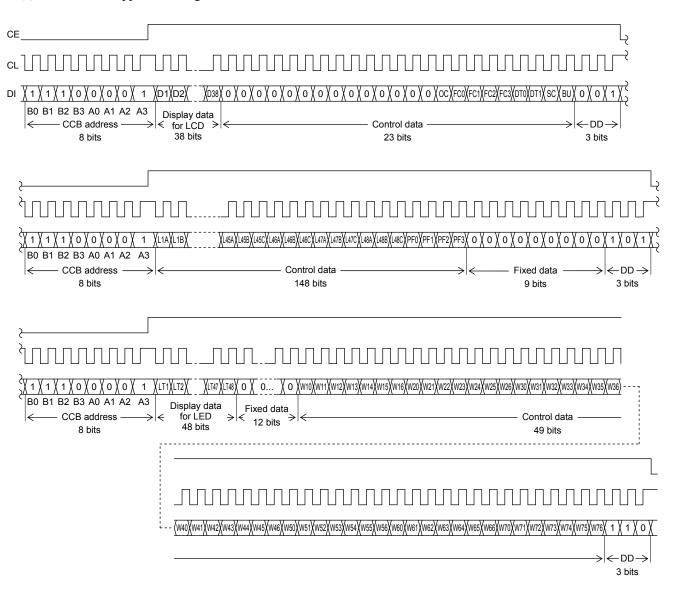

1/4 Duty Drive

(1) When CL is stopped at the low level

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| CCB address               | "87H"                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D140              | Display data for LCD                                                                            |

| • OC                      | Control data for switch of internal oscillator operating mode and external clock operating mode |

| • FC0 to FC3              | Control data for setting of the frame frequency of common and segment output waveform           |

| • DT0, DT1                | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

| • SC                      | Control data for turning on/off segments                                                        |

| • BU                      | Control data for switch of Normal mode and Power-saving mode                                    |

| • L1A, L1B, L1C to L48A,  | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C                |                                                                                                 |

| • PF0 to PF3              | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48             | Display data for LED                                                                            |

| • W10 to W16, W20 to W26, | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46,   |                                                                                                 |

| W50 to W56, W60 to W66    |                                                                                                 |

| W70 to W76                |                                                                                                 |

# (2) When CL is stopped at the high level

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| • CCB address             | "87H"                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D140              | Display data for LCD                                                                            |

| • OC                      | Control data for switch of internal oscillator operating mode and external clock operating mode |

| • FC0 to FC3              | Control data for setting of the frame frequency of common and segment output waveform           |

| • DT0, DT1                | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

| • SC                      | Control data for turning on/off segments                                                        |

| • BU                      | Control data for switch of Normal mode and Power-saving mode                                    |

| • L1A, L1B, L1C to L48A,  | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C                |                                                                                                 |

| • PF0 to PF3              | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48             | Display data for LED                                                                            |

| • W10 to W16, W20 to W26, | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46,   |                                                                                                 |

| W50 to W56, W60 to W66    |                                                                                                 |

| W70 to W76                |                                                                                                 |

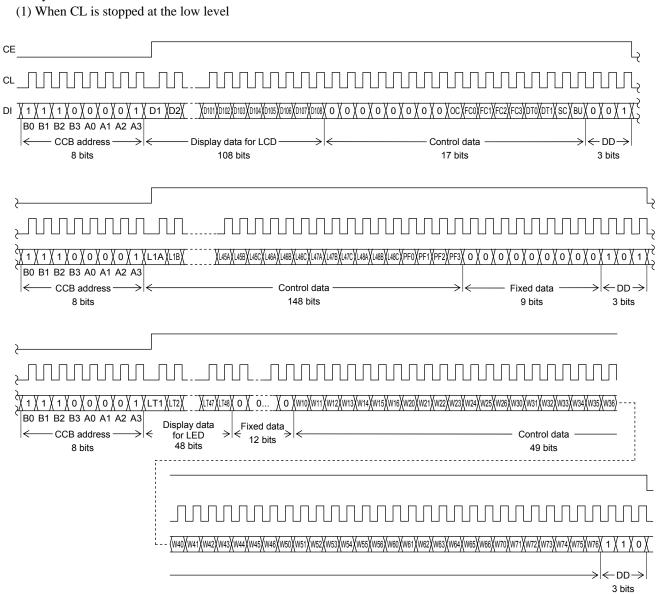

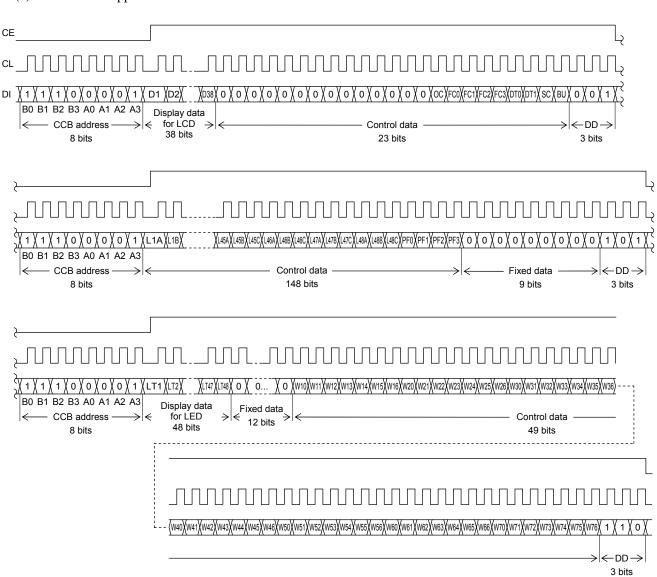

# 1/3 Duty Drive

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| CCB address               | "87H"                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D108              | Display data for LCD                                                                            |

| • OC                      | Control data for switch of internal oscillator operating mode and external clock operating mode |

| • FC0 to FC3              | Control data for setting of the frame frequency of common and segment output waveform           |

| • DT0, DT1                | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

|                           | Control data for turning on/off segments                                                        |

| • BU                      | Control data for switch of Normal mode and Power-saving mode                                    |

| • L1A, L1B, L1C to L48A,  | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C                |                                                                                                 |

| • PF0 to PF3              | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48             | Display data for LED                                                                            |

| • W10 to W16, W20 to W26, | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46,   |                                                                                                 |

| W50 to W56, W60 to W66    |                                                                                                 |

| W70 to W76                |                                                                                                 |

# (2) When CL is stopped at the high level

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| CCB address               | "87H"                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D108              | Display data for LCD                                                                            |

| • OC                      | Control data for switch of internal oscillator operating mode and external clock operating mode |

| • FC0 to FC3              | Control data for setting of the frame frequency of common and segment output waveform           |

| • DT0, DT1                | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

| • SC                      | Control data for turning on/off segments                                                        |

| • BU                      | Control data for switch of Normal mode and Power-saving mode                                    |

| • L1A, L1B, L1C to L48A,  | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C                |                                                                                                 |

| • PF0 to PF3              | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48             | Display data for LED                                                                            |

| • W10 to W16, W20 to W26, | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46,   |                                                                                                 |

| W50 to W56, W60 to W66    |                                                                                                 |

| W70 to W76                |                                                                                                 |

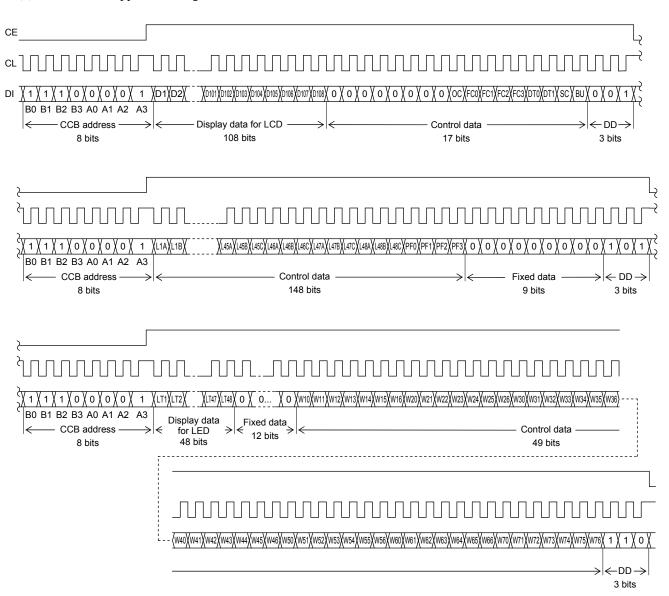

# 1/2 Duty Drive

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| • CCB address             | "87H"                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D74               | Display data for LCD                                                                            |

| • OC                      | Control data for switch of internal oscillator operating mode and external clock operating mode |

| • FC0 to FC3              | Control data for setting of the frame frequency of common and segment output waveform           |

| • DT0, DT1                | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

| • SC                      | Control data for turning on/off segments                                                        |

| • BU                      | Control data for switch of Normal mode and Power-saving mode                                    |

| • L1A, L1B, L1C to L48A,  | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C                |                                                                                                 |

| • PF0 to PF3              | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48             | Display data for LED                                                                            |

| • W10 to W16, W20 to W26, | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46,   |                                                                                                 |

| W50 to W56, W60 to W66    |                                                                                                 |

| W70 to W76                |                                                                                                 |

# (2) When CL is stopped at the high level

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| • CCB address             | "87H"                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D74               | Display data for LCD                                                                            |

| • OC                      | Control data for switch of internal oscillator operating mode and external clock operating mode |

| • FC0 to FC3              | Control data for setting of the frame frequency of common and segment output waveform           |

| • DT0, DT1                | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

| • SC                      | Control data for turning on/off segments                                                        |

| • BU                      | Control data for switch of Normal mode and Power-saving mode                                    |

| • L1A, L1B, L1C to L48A,  | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C                |                                                                                                 |

| • PF0 to PF3              | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48             | Display data for LED                                                                            |

| • W10 to W16, W20 to W26, | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46,   |                                                                                                 |

| W50 to W56, W60 to W66    |                                                                                                 |

| W70 to W76                |                                                                                                 |

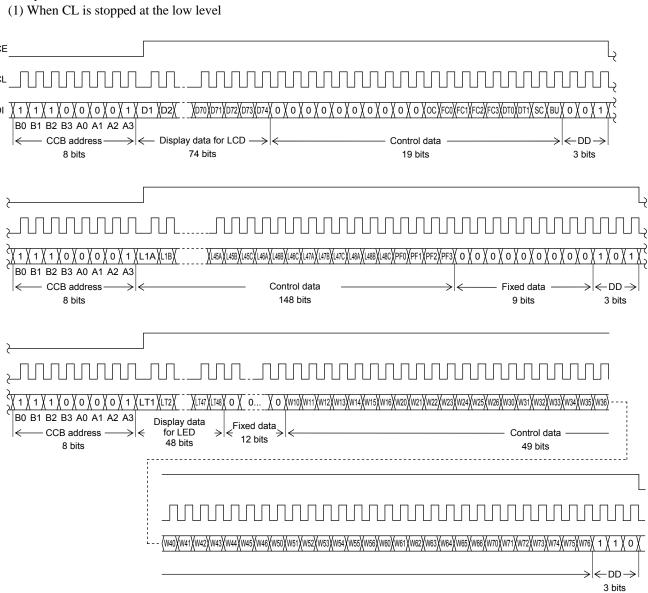

Static Drive (1/1 Duty Drive)

(1) When CL is stopped at the low level

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| • FC0 to FC3            | Display data for LCD Control data for switch of internal oscillator operating mode and external clock operating mode Control data for setting of the frame frequency of common and segment output waveform Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD Control data for turning on/off segments Control data for switch of Normal mode and Power-saving mode Control data for Ch settings of PWM circuits that adjust brightness of LED |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Control data for setting of the frame frequency of LED driver output waveform                                                                                                                                                                                                                                                                                                                                                                                                         |

| • LT1 to LT48           | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                         | PWM data of PWM circuits of LED driver output                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| W30 to W36, W40 to W46, |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| W50 to W56, W60 to W66  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| W70 to W76              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# (2) When CL is stopped at the high level

(Note 1) The input of serial data is taken in at the rising edge of CL, and latched at the falling edge of CE. In addition, this IC has the function that counts the number of CL clock to receive the correct serial data. That is to say, because it isn't latched at the falling edge of CE when the number of the count of CL in each serial data is wrong, receiving wrong serial data can be prevented.

| CCB address               | "87H"                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------|

| • D1 to D38               | Display data for LCD                                                                            |

| • OC                      | Control data for switch of internal oscillator operating mode and external clock operating mode |

| • FC0 to FC3              | Control data for setting of the frame frequency of common and segment output waveform           |

| • DT0, DT1                | Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD       |

| • SC                      | Control data for turning on/off segments                                                        |

| • BU                      | Control data for switch of Normal mode and Power-saving mode                                    |

| • L1A, L1B, L1C to L48A,  | Control data for Ch settings of PWM circuits that adjust brightness of LED                      |

| L48B, L48C                |                                                                                                 |

| • PF0 to PF3              | Control data for setting of the frame frequency of LED driver output waveform                   |

| • LT1 to LT48             | Display data for LED                                                                            |

| • W10 to W16, W20 to W26, | PWM data of PWM circuits of LED driver output                                                   |

| W30 to W36, W40 to W46,   |                                                                                                 |

| W50 to W56, W60 to W66    |                                                                                                 |

| W70 to W76                |                                                                                                 |

#### **Control data Functions**

(1) OC ... Control data for switch of internal oscillator operating mode and external clock operating mode. This control data bit selects either the internal oscillator operating mode or external clock operating mode.

| ОС | Fundamental clock operating mode   | Input pin (OSCI) state                                                |

|----|------------------------------------|-----------------------------------------------------------------------|

| 0  | Internal oscillator operating mode | Connect to GND                                                        |

| 1  | External clock operating mode      | Input the clock (f <sub>CK</sub> = 100 to 600 [kHz]) from the outside |

(2) FC0 to FC3 ... Control data for setting of the frame frequency of common and segment output waveform.

|     |                |   |     | Frame frequency of common and segment output waveform fo [Hz]                         |                                                                                       |  |

|-----|----------------|---|-----|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|

| FC0 | CO FC1 FC2 FC3 |   | FC3 | Internal oscillator operating mode<br>(Control data OC ="0",<br>fosc = 300 [kHz] typ) | External clock operating mode (Control data OC ="1", f <sub>CK</sub> = 300 [kHz] typ) |  |

| 0   | 0              | 0 | 0   | fosc/4992                                                                             | f <sub>CK</sub> /4992                                                                 |  |

| 1   | 0              | 0 | 0   | fosc/4608                                                                             | f <sub>CK</sub> /4608                                                                 |  |

| 0   | 1              | 0 | 0   | fosc/4224                                                                             | f <sub>CK</sub> /4224                                                                 |  |

| 1   | 1              | 0 | 0   | fosc/3840                                                                             | f <sub>CK</sub> /3840                                                                 |  |

| 0   | 0              | 1 | 0   | fosc/3456                                                                             | f <sub>CK</sub> /3456                                                                 |  |

| 1   | 0              | 1 | 0   | fosc/3072                                                                             | f <sub>CK</sub> /3072                                                                 |  |

| 0   | 1              | 1 | 0   | fosc/2688                                                                             | f <sub>CK</sub> /2688                                                                 |  |

| 1   | 1              | 1 | 0   | fosc/2496                                                                             | f <sub>CK</sub> /2496                                                                 |  |

| 0   | 0              | 0 | 1   | fosc/2448                                                                             | f <sub>CK</sub> /2448                                                                 |  |

| 1   | 0              | 0 | 1   | fosc/2304                                                                             | f <sub>CK</sub> /2304                                                                 |  |

| 0   | 1              | 0 | 1   | fosc/2112                                                                             | f <sub>CK</sub> /2112                                                                 |  |

| 1   | 1              | 0 | 1   | fosc/1920                                                                             | f <sub>CK</sub> /1920                                                                 |  |

| 0   | 0              | 1 | 1   | fosc/1728                                                                             | f <sub>CK</sub> /1728                                                                 |  |

| 1   | 0              | 1 | 1   | fosc/1536 f <sub>CK</sub> /1536                                                       |                                                                                       |  |

| 0   | 1              | 1 | 1   | fosc/1344                                                                             | f <sub>CK</sub> /1344                                                                 |  |

| 1   | 1              | 1 | 1   | fosc/1152                                                                             | f <sub>CK</sub> /1152                                                                 |  |

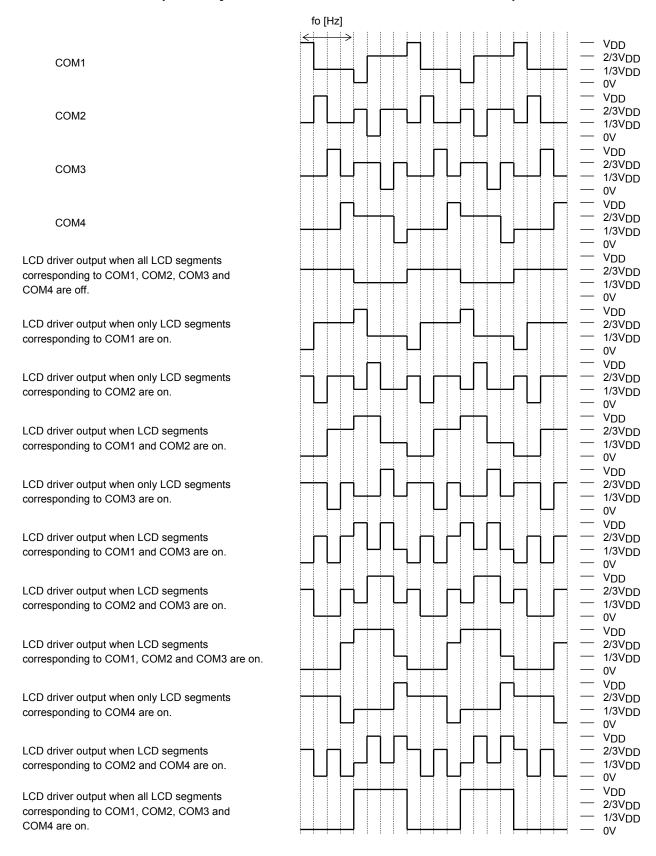

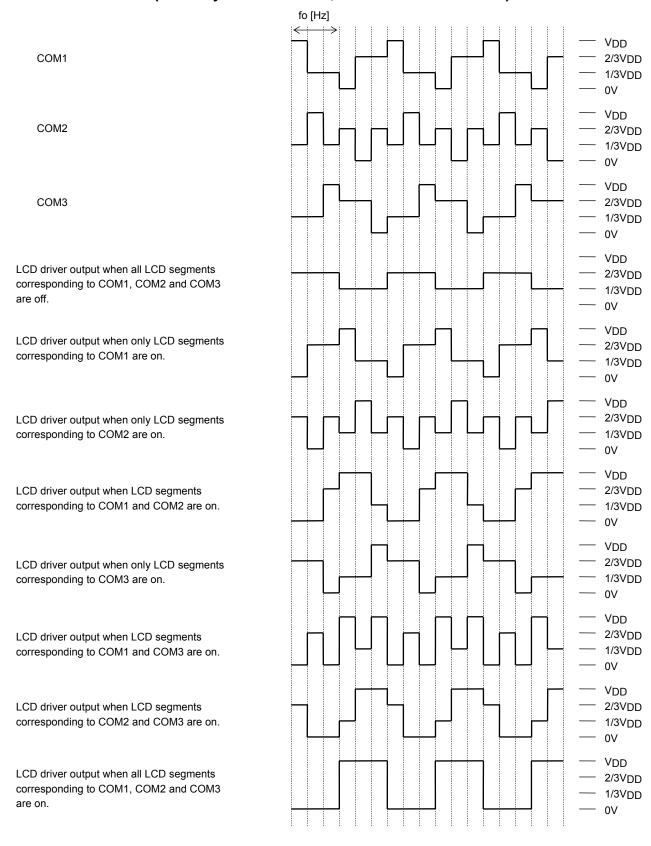

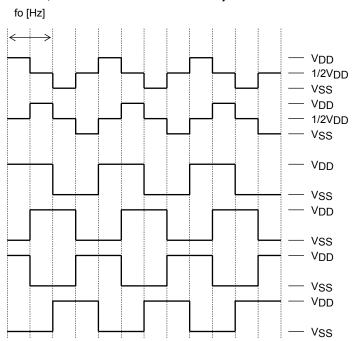

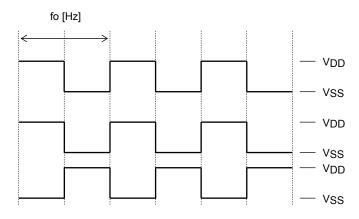

(3) DT0, DT1 ... Control data for setting of drive scheme (setting of 1/1 to 1/4 Duty Drive scheme) of LCD These control bits select 1/4-Duty 1/3-Bias Drive, 1/3-Duty 1/3-Bias Drive, 1/2-Duty 1/2-Bias Drive, or Static Drive (1/1-Duty Drive) of LCD.

|     | 2 miles = 11 ( 1 / 1 = 1 mj = 11 / 1 / 1 = 1 = 1 |                               |                |          |          |  |  |  |

|-----|--------------------------------------------------|-------------------------------|----------------|----------|----------|--|--|--|

| DTO | DT4                                              | Discrete metal CD             | Each pin state |          |          |  |  |  |

| DT0 | DT0 DT1                                          | Drive scheme for LCD          | COM2/S38       | COM3/S37 | COM4/S36 |  |  |  |

| 0   | 0                                                | 1/4-Duty 1/3-Bias Drive       | COM2           | COM3     | COM4     |  |  |  |

| 1   | 0                                                | 1/3-Duty 1/3-Bias Drive       | COM2           | COM3     | S36      |  |  |  |

| 0   | 1                                                | 1/2-Duty 1/2-Bias Drive       | COM2           | S37      | S36      |  |  |  |

| 1   | 1                                                | Static Drive (1/1-Duty Drive) | S38            | S37      | S36      |  |  |  |

Note) COM2 to COM4: Common output / S38 to S36: Segment output

(4) SC ... Control data for turning on/off segments

This control data bit controls the on/off state of the segments.

| SC | Display state |

|----|---------------|

| 0  | On            |

| 1  | Off           |

Note that when the segments are turned off by setting SC to 1, the segments are turning off by outputting segment off waveforms from the segment output pins.

(5) BU ... Control data for switch of Normal mode and Power-saving mode

This control data bit selects either Normal mode or Power-saving mode.

| BU | Mode                                                                                                                                                                                                                                                                                                                                                     |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | Normal mode                                                                                                                                                                                                                                                                                                                                              |

| 1  | Power-saving mode  The oscillation of internal oscillator circuit is stopped when internal oscillator operating mode (OC = [0]), and the receiving of external clock isn't admitted when external clock operating mode (OC = [1]). In addition, common and segment output pins are V <sub>SS</sub> level, and LED driver output pins are High impedance. |

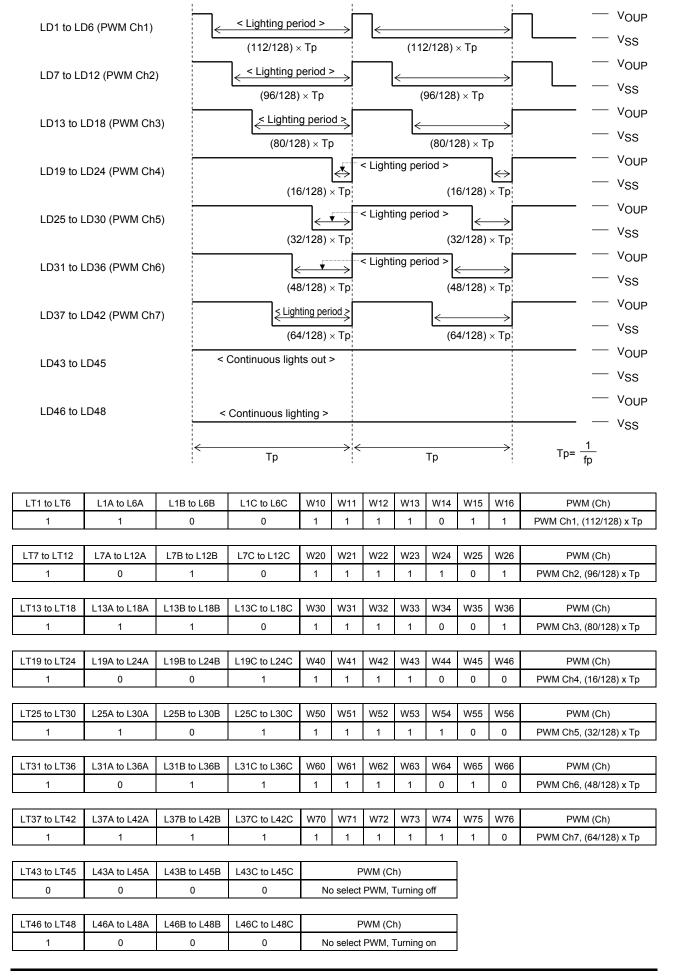

(6) L1A, L1B, L1C to L48A, L48B, L48C ... Control data for Ch settings of PWM circuits that adjust brightness of LED These control data bits set the Ch of PWM circuit for LED driver output pins, LD1 to LD48.

| LnA | LnB | LnC | Ch of PWM circuit for LED driver output LDn                                                                            |

|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | 0   | PWM circuit is not selected. (The setting of turning on/off of the duty 100% by Display data LTn for LED is possible.) |

| 1   | 0   | 0   | PWM circuit (Ch1) is selected.                                                                                         |

| 0   | 1   | 0   | PWM circuit (Ch2) is selected.                                                                                         |

| 1   | 1   | 0   | PWM circuit (Ch3) is selected.                                                                                         |

| 0   | 0   | 1   | PWM circuit (Ch4) is selected.                                                                                         |

| 1   | 0   | 1   | PWM circuit (Ch5) is selected.                                                                                         |

| 0   | 1   | 1   | PWM circuit (Ch6) is selected.                                                                                         |

| 1   | 1   | 1   | PWM circuit (Ch7) is selected.                                                                                         |

Note) LnA, LnB, LnC (n = 1 to 48) data are control data that set the Ch of PWM circuit for LED driver output pins LDn (n = 1 to 48).

For example, if (L1A, L1B, L1C) = (1, 0, 0), (L11A, L11B, L11C) = (1, 1, 0) and (L21A, L21B, L21C) = (0, 1, 1) is set, LED driver output pin LD1 select PWM circuit (Ch1) and LED driver output pin LD11 select PWM circuit (Ch3) and LED driver output pin LD21 select PWM circuit (Ch6).

(7) PF0 to PF3 ... Control data for setting of the frame frequency of LED driver output waveform These control data bits set the frame frequency of LED driver output waveform of LED output pin setting PWM circuit (Ch1 to Ch7).

|     |     | PF2 PF3 |   | Frame frequency of LED driver                                                   | output waveform fp [Hz]                                                                |

|-----|-----|---------|---|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| PF0 | PF1 |         |   | Internal oscillator operating mode (Control data OC ="0", fosc = 300 [kHz] typ) | External clock operating mode (Control data OC ="1",  f <sub>CK</sub> = 300 [kHz] typ) |

| 0   | 0   | 0       | 0 | fosc/1664                                                                       | f <sub>CK</sub> /1664                                                                  |

| 1   | 0   | 0       | 0 | fosc/1536                                                                       | f <sub>CK</sub> /1536                                                                  |

| 0   | 1   | 0       | 0 | fosc/1408                                                                       | f <sub>CK</sub> /1408                                                                  |

| 1   | 1   | 0       | 0 | fosc/1280                                                                       | f <sub>CK</sub> /1280                                                                  |

| 0   | 0   | 1       | 0 | fosc/1152                                                                       | f <sub>CK</sub> /1152                                                                  |

| 1   | 0   | 1       | 0 | fosc/1024                                                                       | f <sub>CK</sub> /1024                                                                  |

| 0   | 1   | 1       | 0 | fosc/896                                                                        | f <sub>CK</sub> /896                                                                   |

| 1   | 1   | 1       | 0 | fosc/768 f <sub>CK</sub> /768                                                   |                                                                                        |

| 0   | 0   | 0       | 1 | fosc/640 f <sub>CK</sub> /640                                                   |                                                                                        |

| 1   | 0   | 0       | 1 | fosc/512                                                                        | f <sub>CK</sub> /512                                                                   |

Note) If (PF0, PF1, PF2, PF3) = (X, 1, 0, 1), (X, X, 1, 1) are set, the frame frequency (fosc/1408, fCK/1408) of setting (PF0, PF1, PF2, PF3) = (0, 1, 0, 0) is selected.

$(8)\ W10\ to\ W16,\ W20\ to\ W26,\ W30\ to\ W36,\ W40\ to\ W46,\ W50\ to\ W56,\ W60\ to\ W66,\ W70\ to\ W76$

... PWM data of PWM circuit for LED driver output

These control data bits set LED lighting time per 1 frame of LED driver output waveform of LED driver output pin setting PWM circuit (Ch1 to Ch7)

| Wn0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | output pin setting PWM circuit (Ch1 to Ch7). |     |     |     |     |     |     |                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----|-----|-----|-----|-----|-----|-------------------------------|

| O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Wn0                                          | Wn1 | Wn2 | Wn3 | Wn4 | Wn5 | Wn6 | LED lighting time per 1 frame |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                            | 0   | 0   | 0   | 0   | 0   | 0   |                               |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                            | 0   | 0   | 0   | 0   | 0   | 0   | (2/128) × Tp                  |

| O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                            | 1   | 0   | 0   | 0   | 0   | 0   |                               |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                            | 1   |     | 0   | 0   | 0   | 0   | (4/128) × Tp                  |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                            | 0   |     | 0   | 0   | 0   | 0   | (5/128) × Tp                  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |     |     |     |     |     |     |                               |

| O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |     |     |     |     |     |     |                               |