Rev V1

#### **Features**

- · One 2A common anode LED/Laser driver

- · Two 1A common anode LED/Laser drivers

- · Laser Despeckle

- · Integrated 30Msps 12bit DACs

- Automatic real time power control (ColorMinder)

- · DC-DC converter reference generators to optimize each laser bias voltage

- High speed 4 wire interface or slave I<sup>2</sup>C for register settings download from uC

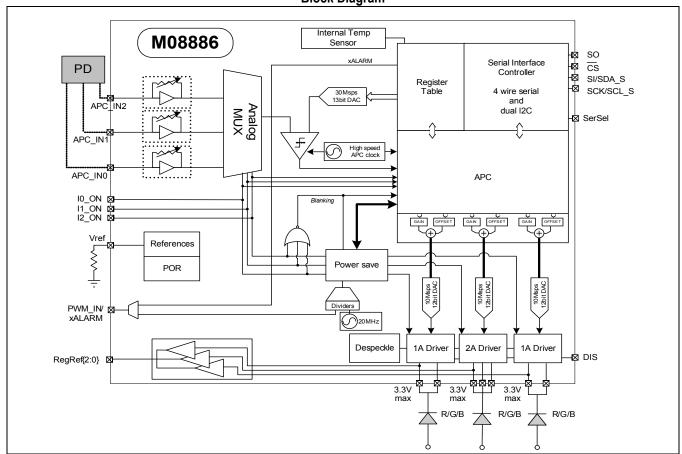

The M08886 is a high efficiency integrated RGB LED/Laser driver with patent pending de-speckle and power save technologies for LCD/LCoS/DLP projection displays. It features ColorMinder - a multilevel automatic laser power control for consistent white balance across temperature variation and laser aging. The M08886 allows for the monitoring of the internal IC junction temperature and the control of external DC-DC converters to generate optimal laser supply.

**Applications**

· LCD/LCoS/DLP Portable and Pico Projectors

#### **Block Diagram**

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice.

Visit www.macom.com for additional data sheets and product information.

For further information and support please visit: <a href="http://www.macom.com/support">http://www.macom.com/support</a>

Rev V1

#### **Ordering Information**

| Part Number | Package | Operating Temperature |  |  |

|-------------|---------|-----------------------|--|--|

| M08886G-13* |         | -40 °C to 85 °C       |  |  |

<sup>\*</sup> The letter "G" designator after the part number indicates that the device is RoHS compliant. The RoHS compliant devices are backwards compatible with 225 °C reflow profiles.

#### **Revision History**

| Revision | Level       | Date           | Description                                                                                                                          |  |  |

|----------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| V1       | Release     | May 2015       | Update register references.                                                                                                          |  |  |

| F (V3P)  | Preliminary | September 2010 | Update specifications to match characterization data. Edit Functional Description and Register sections.                             |  |  |

| D (V2P)  | Preliminary | June 2010      | Corrected pin 21 and 22 description in Table 1-11.                                                                                   |  |  |

| C (V1P)  | Preliminary | May 2010       | Remove support for external EEPROM and Analog APC. Power dissipation and APC specifications updated. Functional Description updated. |  |  |

| B (V2A)  | Advance     | June 2009      | Changed Format, content unchanged                                                                                                    |  |  |

| A (V1A)  | Advance     | March 2009     | Initial release.                                                                                                                     |  |  |

#### **Datasheet Font Conventions**

| Font            | Example               | Explanation                                                                                                                                                                                                    |

|-----------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Italics         | IOUT0                 | Words in Italics designate M08886 pins. In this case pin IOUT0.                                                                                                                                                |

| Bold letter "x" | IOUTX apcx ctrl0[2:1] | A letter "x" or "X" in bold font is a placeholder for channel 0, 1 or 2. When an "x" is used the information applies to all 3 channels.                                                                        |

|                 |                       | IOUTX can mean IOUT0, IOUT1 or IOUT2 or it can mean OUT0, IOUT1 and IOUT2 depending on the context.                                                                                                            |

|                 |                       | $apc \textbf{x}\_ctrl0[2:1] \ can \ mean \ registers \ apc0\_ctrl0[2:1], \ apc1\_ctrl0[2:1] \ or \ registers \ apc0\_ctrl0[2:1], \ apc1\_ctrl0[2:1] \ and \ apc2\_ctrl0[2:1] \ depending \ on \ the \ context$ |

## **Table of Contents**

| Order   | ing In  | tormation                                                           | 2   |

|---------|---------|---------------------------------------------------------------------|-----|

| Revis   | ion Hi  | story                                                               | 2   |

| Datas   | sheet I | Font Conventions                                                    | 2   |

|         |         | ontents                                                             |     |

|         |         |                                                                     |     |

|         | _       | res                                                                 |     |

| List of | f Tabl  | es                                                                  | 6   |

| 1.0     | Produ   | uct Specification                                                   | 7   |

|         | 1.1     | Absolute Maximums                                                   | . 7 |

|         | 1.2     | DC Characteristics                                                  | 3.  |

|         | 1.3     | Target DAC (RGB sensor target current)                              | . 9 |

|         | 1.4     | Laser Current DACs1                                                 | (   |

|         | 1.5     | Laser Drivers1                                                      | 2   |

|         | 1.6     | DC-DC Converters Reference Generators                               | 2   |

|         | 1.7     | APC Input Characteristics                                           |     |

|         | 1.8     | CMOS Pins Characteristics                                           |     |

|         | 1.9     | Slave I2C Timing Specifications1,2                                  |     |

|         | 1.10    | High Speed Serial Interface Timing Specifications                   |     |

|         | 1.11    | M08886 Pinout                                                       |     |

|         |         | Pin List and Descriptions                                           |     |

|         | 1.13    | Package Information                                                 | 22  |

| 2.0     | Func    | tional Description                                                  | 2   |

|         | 2.1     | Automatic Power Control (APC)                                       | 23  |

|         |         | 2.1.1 Simple Implementation of APC Control                          | 24  |

|         |         | 2.1.2 Highly Featured Implementation of APC Control                 |     |

|         |         | 2.1.3 Compensating the TIA at the Photodetector Input               |     |

|         | 2.2     | 2.1.4 Laser Offset (threshold) Tracking with APC                    |     |

|         | 2.2     | 2.2.1 Increasing the Maximum LED/Drive Current by Combining Outputs |     |

|         | 2.3     | Laser\LED Voltage Supply Control.                                   |     |

|         | 2.4     | Pulse Width Modulation (PWM)                                        |     |

|         | 2.5     | Multi Pulse Generator (MPG)                                         |     |

## M08886-13

| Hig | h Per | tormance RGB LED/Laser Driver for LCD/LCoS/DLP Projection Displays | Rev V1 |

|-----|-------|--------------------------------------------------------------------|--------|

|     |       | D 0 5 1                                                            | -      |

|     | 2.6   | Power Save Features                                                |        |

|     | 2.7   | Safety                                                             |        |

|     | 2.8   | Programmable Serial Interface                                      | 34     |

|     | 2.9   | Driving a String of LEDs from a High Voltage Supply                | 34     |

|     | 2.10  | Power Sequencing                                                   | 36     |

|     | 2.11  | Layout Considerations                                              | 36     |

| 3 N | Regi  | sters                                                              | 37     |

Rev V1

## **List of Figures**

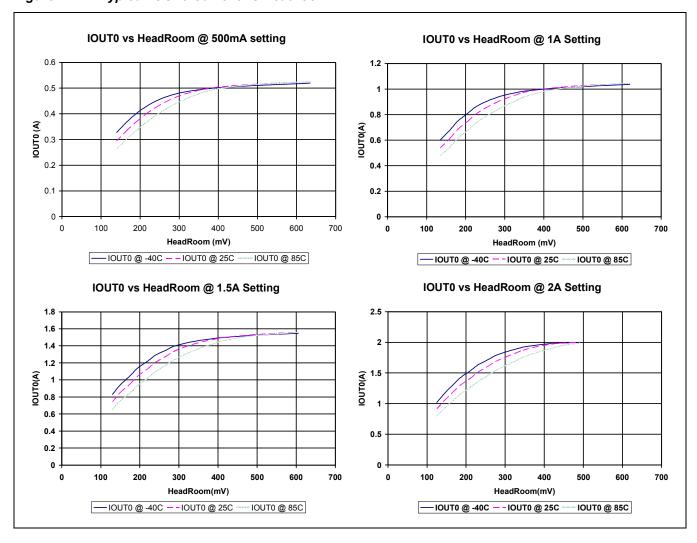

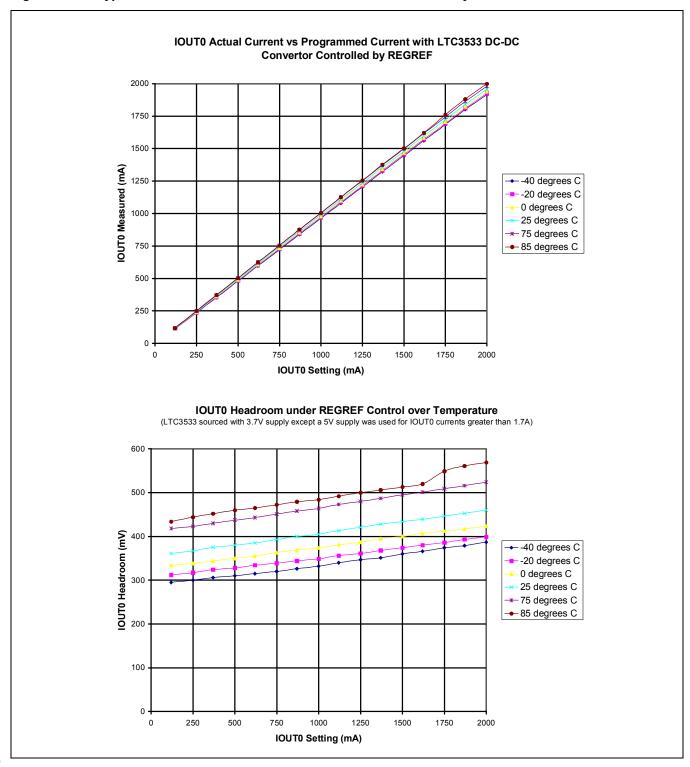

| Figure 1-1.  | Typical IOUT0 Current vs Headroom                                | . 11 |

|--------------|------------------------------------------------------------------|------|

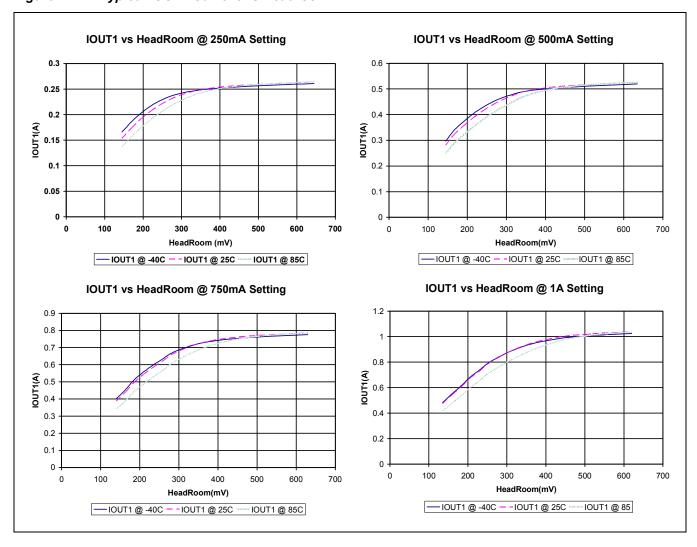

| Figure 1-2.  | Typical IOUT1 Current vs Headroom                                | . 12 |

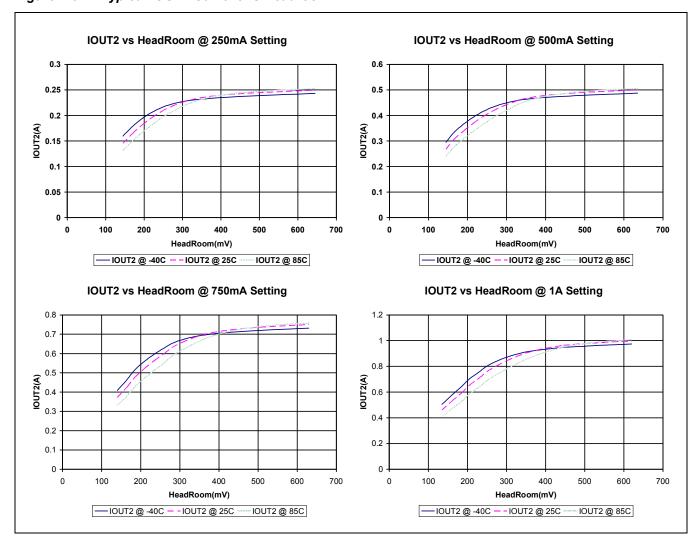

| Figure 1-3.  | Typical IOUT2 Current vs Headroom                                | . 13 |

| Figure 1-4.  | Typical IOUT0 Current with DC-DC Converter Controlled by REGREF0 | . 15 |

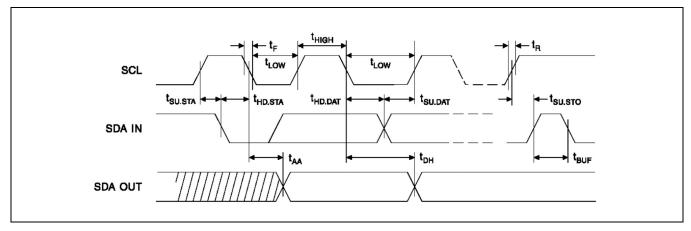

| Figure 1-5.  | Slave I2C Timing                                                 | . 17 |

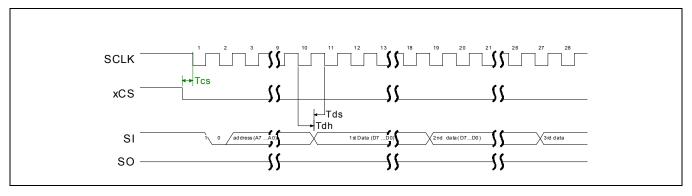

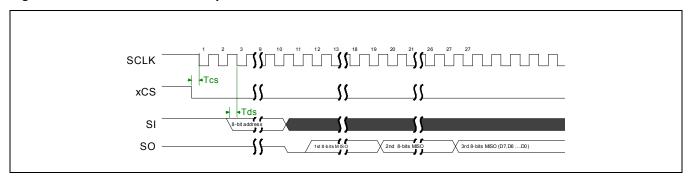

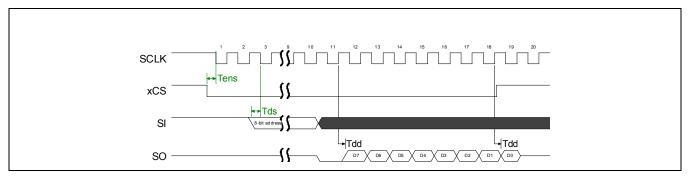

| Figure 1-6.  | Serial Interface Sequential Write                                | . 18 |

| Figure 1-7.  | Serial Interface Random Write                                    | . 18 |

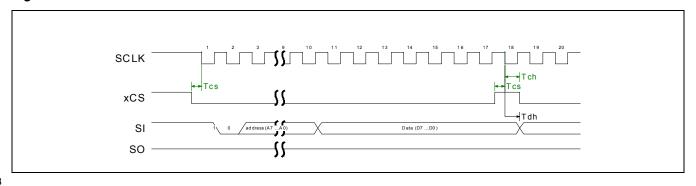

| Figure 1-8.  | Serial Interface Sequential Read                                 | . 19 |

| Figure 1-9.  | Serial Interface Random Read                                     | . 19 |

| Figure 1-10. | M08886 Pinout                                                    | . 20 |

| Figure 1-11. | Sawn QFN32 Package Information                                   | . 22 |

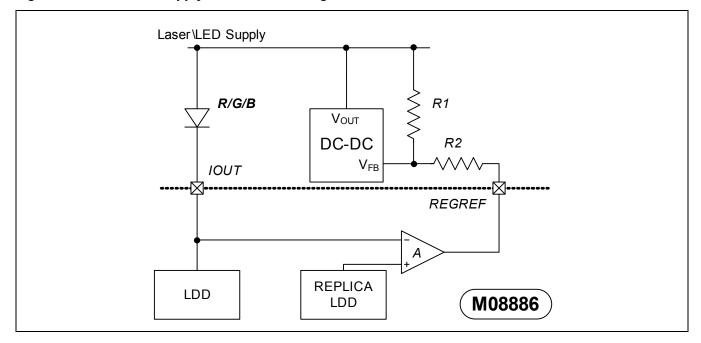

| Figure 2-1.  | laser/led Supply Control Block Diagram                           | . 29 |

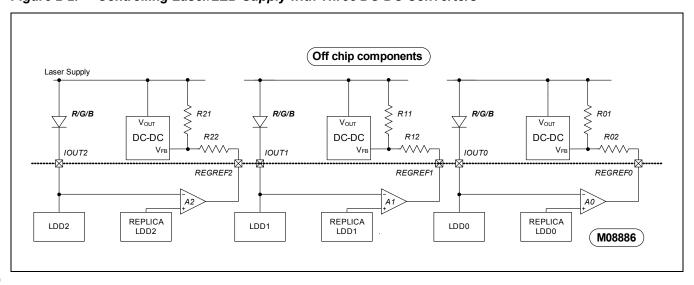

| Figure 2-2.  | Controlling Laser/LED Supply with Three DC-DC Converters         | . 29 |

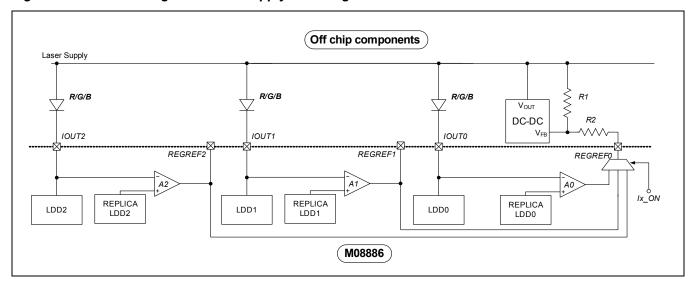

| Figure 2-3.  | Controlling Laser/LED Supply with Single DC-DC Converter         | . 30 |

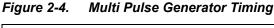

| Figure 2-4.  | Multi Pulse Generator Timing.                                    | . 32 |

| Figure 2-5.  | Driving a String of LEDs from a High Voltage Supply              | . 35 |

| Figure 2-6.  | Power-Up                                                         | . 36 |

| Figure 2-7   | Power-Down                                                       | 36   |

## M08886-13

### High Performance RGB LED/Laser Driver for LCD/LCoS/DLP Projection Displays

Rev V1

## **List of Tables**

| Table 1-1.  | Absolute Maximum Ratings                                           | 1    |

|-------------|--------------------------------------------------------------------|------|

| Table 1-2.  | DC Characteristics                                                 | 8    |

| Table 1-3.  | Register Settings used for Measurements in Various Operating Modes | 9    |

| Table 1-4.  | Target DAC                                                         | 9    |

| Table 1-5.  | Laser Current DACs                                                 | . 10 |

| Table 1-6.  | Laser Drivers                                                      | . 14 |

| Table 1-7.  | DC-DC Converters Reference Generators                              | . 14 |

| Table 1-8.  | APC Input Characteristics                                          | . 16 |

| Table 1-9.  | CMOS Pins Characteristics                                          | . 16 |

| Table 1-10. | Slave I2C Timing Specifications.                                   | . 17 |

| Table 1-11. | High Speed Serial Interface Timing Specifications                  | . 18 |

| Table 1-12. | Pin List and Descriptions                                          | . 2  |

| Table 2-1.  | Basic Register Configuration for APC Control                       | . 24 |

| Table 2-2.  | Highly Featured Register Configuration for APC Control             | . 25 |

| Table 2-3.  | Clock Selection for PWM and MPG                                    | . 3′ |

| Table 3-1.  | M08886 Registers                                                   | . 37 |

## 1.0 Product Specification

#### 1.1 Absolute Maximums

These are the absolute maximum ratings at or beyond which the IC can be expected to fail or be damaged. Reliable operation at these extremes for any length of time is not implied.

Table 1-1. Absolute Maximum Ratings

| Symbol                                                             | Parameter                                           | Rating                          | Units |

|--------------------------------------------------------------------|-----------------------------------------------------|---------------------------------|-------|

| DV <sub>DD</sub> , ALV <sub>DD</sub>                               | 1.8 V Digital and Analog Supplies                   | 1.98                            | V     |

| DHV <sub>DD,</sub> AHV <sub>DD</sub>                               | 3.3 V Digital and Analog Supplies                   | 3.63                            | V     |

| IOUT0, IOUT1, IOUT2                                                | Output pins for driving LED/Laser - maximum voltage | 3.3                             | V     |

| T <sub>JCTN</sub>                                                  | Junction Temperature                                | -40 to +125                     | °C    |

| T <sub>STG</sub>                                                   | Storage Temperature                                 | -65 to +150                     | °C    |

| I <sup>2</sup> C/SPI                                               | Serial data format select input                     | -0.4 to 3                       | V     |

| APC_IN0, APC_IN1, APC_IN2                                          | RGB Photodiode Feedback Input Voltage               | -0.4 to ALV <sub>DD</sub> + 0.4 | V     |

| I <sub>APC_IN0</sub> , I <sub>APC_IN1</sub> , I <sub>APC_IN2</sub> | RGB Photodiode Feedback Input Current               | -0.5 to 4                       | mA    |

| I_VREF                                                             | Current into Reference Voltage Pin                  | -0.12 to +0.12                  | mA    |

| DIS                                                                | Disable all LED/Laser outputs                       | -0.4 to 3                       | V     |

| I0_ON, I1_ON, I2_ON                                                | Enable LED/Laser output                             | -0.4 to 3                       | V     |

| CLK_IN, CS, SI, SCLK, SO                                           | SPI inputs and output                               | -0.4 to 3                       | V     |

| SCLK_S, SDA_S                                                      | I <sup>2</sup> C interface                          | -0.4 to 3                       | V     |

| REGREF_0, REGREF_1, REGREF_2                                       | External DC-DC converter control signal             | -0.4 to DV <sub>DD</sub> +0.4   | V     |

| I_REGREF_0, I_REGREF_1, I_REGREF_2                                 | Current into or out of REGREFX pins                 | -0.12 to +0.12                  | mA    |

Rev V1

#### 1.2 DC Characteristics

**Min and Max values:** Tc= -40 °C to 85 °C,  $DV_{DD}$ =1.8 V+/-5%,  $ALV_{DD}$ =1.8 V+/-5%,  $DHV_{DD}$ =3.3 V+/-5%,

$AHV_{DD}$  =3.3 V+/-5% unless otherwise noted.

**Typical values:** Tc=25 °C, DV<sub>DD</sub>=1.8 V, ALV<sub>DD</sub>=1.8 V, DHV<sub>DD</sub> =3.3 V, AHV<sub>DD</sub> =3.3 V unless otherwise noted.

Table 1-2. DC Characteristics

| Symbol            | PARAMETER                                                                                                             | CONDITIONS                     | Min  | Тур  | Max  | Units |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------|------|------|------|-------|

| DV <sub>DD</sub>  | 1.8 V supply for digital circuitry                                                                                    |                                | 1.71 | 1.8  | 1.89 | V     |

| ALV <sub>DD</sub> | 1.8 V supply for analog circuitry                                                                                     |                                | 1.71 | 1.8  | 1.89 | ٧     |

| $DHV_DD$          | 3.3 V supply for digital circuitry                                                                                    |                                | 3.13 | 3.3  | 3.47 | V     |

| $AHV_DD$          | 3.3 V supply for analog circuitry                                                                                     |                                | 3.13 | 3.3  | 3.47 | V     |

| I <sub>LVDD</sub> | LED Mode Supply Current - 1.8 V                                                                                       | Open Loop LED Mode             |      | 17   | 27   | mA    |

|                   | (DV <sub>DD</sub> and ALV <sub>DD</sub> ) <sup>1</sup>                                                                | Closed Loop LED Mode           |      | 31.5 | 45   |       |

|                   | Laser Mode Supply Current - 1.8 V (DV <sub>DD</sub> and ALV <sub>DD</sub> ) <sup>1</sup> (Despeckle enabled on IOUT0) | Open Loop Laser Mode           |      | 42   | 55   |       |

|                   |                                                                                                                       | Closed Loop Laser Mode         |      | 53   | 87   |       |

|                   | Standby Current - 1.8 V                                                                                               | Standby Mode                   |      | 5    |      |       |

| I <sub>HVDD</sub> | LED Mode Supply Current - 3.3 V (DHV <sub>DD</sub> and AHV <sub>DD</sub> ) <sup>1</sup>                               | Open Loop LED Mode             |      | 7    | 11.1 | mA    |

|                   |                                                                                                                       | Closed Loop LED Mode           |      | 7    | 12.1 |       |

|                   | Laser Mode Supply Current - 3.3 V                                                                                     | Closed Loop Laser Mode         |      | 21.5 | 36   |       |

|                   | (DHV <sub>DD</sub> and AHV <sub>DD</sub> ) <sup>1</sup><br>(Despeckle enabled on IOUT0)                               | Closed Loop Laser Mode         |      | 20   | 35   |       |

|                   | Standby Current - 3.3 V                                                                                               |                                |      | 0.05 |      |       |

| Tc                | Case Temp.                                                                                                            | Measured on top of M08886 case | -40  |      | 85   | °C    |

| NOTEC:            | 1                                                                                                                     | 1                              | •    |      | •    |       |

#### NOTES:

<sup>&</sup>lt;sup>1</sup> Excludes serial interface (SPI/I<sup>2</sup>C) current and LED/Laser current

Rev V1

Table 1-3. Register Settings used for Measurements in Various Operating Modes

| Operating Mode         | Register Settings                                                                                                                                                                                                                                  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open Loop LED Mode     | 0x00h=40h, 0x02h=08h, 0x08h=0Fh, 0x09h=0Eh, 0x0Fh=0Ah, 0x0Ah=0Eh, 0x0Bh=0Eh, 0x0Eh=01h, 0x1Ah=00h, 0x1Dh=00h, 0x26h=FFh, 0x28h=03h, 0x40h= 06h                                                                                                     |

| Open Loop Laser Mode   | 0x00h=40h, 0x02h=00h, 0x08h=0Fh, 0x09h=0Eh, 0x0Ah=0Eh, 0x0Bh=0Eh, 0x0Eh=01h, 0x0Fh=0Ah, 0x17h=40h, 0x18h=00h, 0x1Ah=54h, 0x1Dh=11h, 0x26h=FFh, 0x28h=00h, 0x40h= 06h                                                                               |

| Standby Mode           | 0x00h=40h, 0x02h=08h, 0x04h=00h, 0x05h=00h, 0x06h=00h, 0x07h=00h, 0x08h=01h, 0x09h=01h, 0x0Ah=01h, 0x0Bh=01h, 0x0Ch=40h, 0x0Eh=01h, 0x0Fh=0Ah, 0x26h=FFh, 0x40h= 06h,0x90h=10h                                                                     |

| Closed Loop LED Mode   | 0x00h=00h, 0x02h=08h, 0x04h=00h, 0x05h=00h, 0x06h=00h, 0x07h=00h, 0x08h=0Fh, 0x09h=0Eh, 0x0Ah=0Eh, 0x0Bh=0Eh 0x0Eh=00h, 0x0Fh=0Ah, 0x1Ah=00h, 0x1Dh=00h, 0x28h=03h, 0x38h=F4h, 0x3Ch=F2h, 0x40h=F0h, 0x41h=3Ch, 0x90h=00h                          |

| Closed Loop Laser Mode | 0x00h=00h, 0x02h=00h, 0x04h=00h, 0x05h=00h, 0x06h=00h, 0x07h=00h, 0x08h=0Fh, 0x09h=0Eh, 0x0Ah=0Eh, 0x0Bh=0Eh<br>0x0Eh=00h, 0x0Fh=0Ah, 0x1Ah=54h, 0x1Dh=11h, 0x28h=00h, 0x32h=0Eh, 0x33h=00h, 0x38h=F4h, 0x3Ch=F2h, 0x40h=F0h, 0x41h=3Ch, 0x90h=00h |

### 1.3 Target DAC (RGB sensor target current)

Typical values: Tc=25 °C, DV<sub>DD</sub>, ALV<sub>DD</sub>=1.8 V, AHV<sub>DD</sub> =3.3 V

Table 1-4. Target DAC

| PARAMETER                                | CONDITIONS | Min | Тур | Max | Units |

|------------------------------------------|------------|-----|-----|-----|-------|

| Resolution                               |            |     | 13  |     | bits  |

| Conversion rate                          |            |     | 30  |     | Msps  |

| Full scale monitor photodetector current |            |     | 3.4 |     | mA    |

| Step size                                |            |     | 412 |     | nA    |

Rev V1

#### 1.4 Laser Current DACs

**Min and Max values:** Tc= -40 °C to 85 °C,  $DV_{DD}$ =1.8 V+/-5%,  $ALV_{DD}$ =1.8 V+/-5%,  $DHV_{DD}$ =3.3 V+/-5%,

$\mathrm{AHV}_{\mathrm{DD}}$  =3.3 V+/-5% unless otherwise noted.

**Typical values:** Tc=25 °C, DV<sub>DD</sub>=1.8 V, ALV<sub>DD</sub>=1.8 V, DHV<sub>DD</sub> =3.3 V, AHV<sub>DD</sub> =3.3 V unless otherwise noted.

Table 1-5. Laser Current DACs

| PARAMETER        | CONDITIONS                                                                                                                                     | Min  | Тур  | Max  | Units |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Resolution       |                                                                                                                                                |      | 12   |      | bits  |

| Conversion rate  |                                                                                                                                                |      | 30   |      | Msps  |

| Full scale IOUT0 | Current sunk at pin IOUT0 with bench power supply sourcing current and voltage adjusted so output headroom is 500 mV                           | 1.85 | 2    | 2.25 | A     |

| Full scale IOUT1 | Current sunk at pin IOUT1 with bench power supply sourcing current and voltage adjusted so output headroom is 500 mV                           | 0.9  | 1.02 | 1.15 | А     |

| Full scale IOUT2 | Current sunk at pin IOUT2 with bench power supply sourcing current and voltage adjusted so output headroom is 500 mV                           | 0.85 | 0.98 | 1.15 | А     |

| IOUT0 step size  | Average step size between 0.5A and 1.5A setting. Current is sourced from a bench power supply with the voltage adjusted for 500 mV headroom.   | _    | 493  | _    | μA    |

| IOUT1 step size  | Average step size between 0.25A and 0.75A setting. Current is sourced from a bench power supply with the voltage adjusted for 500 mV headroom. | _    | 249  | _    | μA    |

| IOUT2 step size  | Average step size between 0.25A and 0.75A setting. Current is sourced from a bench power supply with the voltage adjusted for 500 mV headroom. | _    | 241  | _    | μA    |

Figure 1-1. Typical IOUT0 Current vs Headroom

Figure 1-2. Typical IOUT1 Current vs Headroom

Figure 1-3. Typical IOUT2 Current vs Headroom

Rev V1

#### 1.5 Laser Drivers

Min and Max values: Tc= -40 °C to 85 °C,  $DV_{DD}$ =1.8 V+/-5%,  $ALV_{DD}$ =1.8 V+/-5%,  $DHV_{DD}$ =3.3 V+/-5%,

$AHV_{DD}$  =3.3 V+/-5% unless otherwise noted.

Typical values: Tc=25 °C, DV<sub>DD</sub>, ALV<sub>DD</sub>=1.8 V, AHV<sub>DD</sub> =3.3 V

#### Table 1-6. Laser Drivers

| PARAMETER                                       | CONDITIONS                               | Min | Тур | Max | Units |

|-------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

| Maximum allowable voltage headroom <sup>1</sup> |                                          |     |     | 3.3 | V     |

| Rise/fall time                                  | 20-80% Into 1 $\Omega$ electrical output |     |     | 5   | ns    |

#### NOTES

#### 1.6 DC-DC Converters Reference Generators

Min and Max values: Tc= -40 °C to 85 °C, DV<sub>DD</sub>=1.8 V+/-5%, ALV<sub>DD</sub>=1.8 V+/-5%, DHV<sub>DD</sub>=3.3 V+/-5%,

AHV<sub>DD</sub> =3.3 V+/-5% unless otherwise noted.

**Typical values:** Tc=25 °C, DV<sub>DD</sub>=1.8 V, ALV<sub>DD</sub>=1.8 V, DHV<sub>DD</sub> =3.3 V, AHV<sub>DD</sub> =3.3 V unless otherwise noted.

Table 1-7. DC-DC Converters Reference Generators

| PARAMETER                | CONDITIONS  | Min | Тур | Max | Units |

|--------------------------|-------------|-----|-----|-----|-------|

| Voltage compliance       | REGREF0,1,2 | 0.3 | 1.2 | 2.9 | V     |

| Maximum load capacitance | REGREF0,1,2 |     |     | 5   | pF    |

| Minimum resistive load   | REGREF0,1,2 | 2.5 |     |     | kΩ    |

<sup>&</sup>lt;sup>1</sup> To prevent damage to the output devices the voltage drop across it cannot exceed 3.3 V. Please refer also to power sequencing paragraph and laser driver paragraph.

Figure 1-4. Typical IOUT0 Current with DC-DC Converter Controlled by REGREF0

Rev V1

#### 1.7 APC Input Characteristics

Min and Max values: Tc= -40 °C to 85 °C, DV<sub>DD</sub>=1.8 V+/-5%, ALV<sub>DD</sub>=1.8 V+/-5%, DHV<sub>DD</sub>=3.3 V+/-5%,

$AHV_{DD}$  =3.3 V+/-5% unless otherwise noted.

**Typical values:** Tc=25 °C, DV<sub>DD</sub>=1.8 V, ALV<sub>DD</sub>=1.8 V, DHV<sub>DD</sub> =3.3 V, AHV<sub>DD</sub> =3.3 V unless otherwise noted.

Table 1-8. APC Input Characteristics

| PARAMETER                   | CONDITIONS  | Min | Тур                  | Max  | Units |

|-----------------------------|-------------|-----|----------------------|------|-------|

| Full scale input            | APC_IN0,1,2 |     | 3.4                  |      | mA    |

| PD capacitance <sup>1</sup> | APC_IN0,1,2 |     |                      | 80   | pF    |

| Input bias                  | APC_IN0,1,2 |     | ALV <sub>DD</sub> /2 |      | V     |

| Maximum Voltage, APC_INX    |             |     |                      | 1.98 | V     |

#### NOTES:

#### 1.8 CMOS Pins Characteristics

Min and Max values: Tc= -40 °C to 85 °C, DV<sub>DD</sub>=1.8 V+/-5%, ALV<sub>DD</sub>=1.8 V+/-5%, DHV<sub>DD</sub>=3.3 V+/-5%,

AHV<sub>DD</sub> =3.3 V+/-5% unless otherwise noted.

**Typical values:** Tc=25 °C, DV<sub>DD</sub>=1.8 V, ALV<sub>DD</sub>=1.8 V, DHV<sub>DD</sub> =3.3 V, AHV<sub>DD</sub> =3.3 V unless otherwise noted.

Table 1-9. CMOS Pins Characteristics

| PARAMETER                    | CONDITIONS                     | Min                   | Тур | Max                   | Units |

|------------------------------|--------------------------------|-----------------------|-----|-----------------------|-------|

| V <sub>IH</sub> <sup>1</sup> |                                | 0.65 DV <sub>DD</sub> |     | 2.75                  | V     |

| V <sub>IL</sub>              |                                | 0                     |     | 0.35 DV <sub>DD</sub> | V     |

| V <sub>OH</sub>              |                                | DV <sub>DD</sub> -0.4 |     | DV <sub>DD</sub>      | V     |

| V <sub>0L</sub>              |                                | 0                     |     | 0.4                   | V     |

| Rise/fall time <sup>2</sup>  | Maximum load of 5 pF. SPI mode |                       | 3   |                       | ns    |

#### **NOTES**

<sup>&</sup>lt;sup>1</sup> Care should be taken in routing of each PD input so that total capacitance on the pin including routing does not exceed 80 pF

<sup>&</sup>lt;sup>1</sup> Digital pins are (1.8 V devices) 2.5 V (+/-10%) tolerant

<sup>&</sup>lt;sup>2</sup> In I<sup>2</sup>C mode rise time depends on load and pull up resistor.

Rev V1

## 1.9 Slave I<sup>2</sup>C Timing Specifications<sup>1,2</sup>

**Typical values:** Tc=25  $^{\circ}$ C, DV<sub>DD</sub>, ALV<sub>DD</sub>=1.8 V, AHV<sub>DD</sub> =3.3 V

Table 1-10. Slave I<sup>2</sup>C Timing Specifications

| Parameter                                                                            | Symbol (refer to figure below) | Min | Тур | Max | Units |

|--------------------------------------------------------------------------------------|--------------------------------|-----|-----|-----|-------|

| Clock Frequency, SCL_S                                                               | f <sub>SCL_SLAVE</sub>         | -   | -   | 3.4 | MHz   |

| Clock Pulse Width Low                                                                | t <sub>LOW</sub>               | 160 | -   | _   | ns    |

| Clock Pulse Width High                                                               | t <sub>HIGH</sub>              | 60  | -   | -   | ns    |

| Clock Low to Data Out Valid                                                          | t <sub>AA</sub>                | 0   | -   | 70  | ns    |

| Start Hold Time                                                                      | thdsta                         | 160 | -   | -   | ns    |

| Start Set-up Time                                                                    | tsusta                         | 160 | -   | -   | ns    |

| Data In Hold Time                                                                    | t <sub>HDDAT</sub>             | 0   | -   | -   | ns    |

| Data In Set-up Time                                                                  | t <sub>SUDAT</sub>             | 10  | -   | -   | ns    |

| Outputs (SDA_M, SCL_M, SDA_S and SCL_S) internal pull-up resistor value <sup>3</sup> | R <sub>PULL-UP</sub>           | -   | 250 | -   | kΩ    |

| Stop Set-up Time                                                                     | t <sub>SUSTO</sub>             | 160 | -   | -   | ns    |

| Data Out Hold Time                                                                   | t <sub>DH</sub>                | 5   | _   | -   | ns    |

| NOTES                                                                                |                                |     |     |     |       |

#### NOTES:

Figure 1-5. Slave I<sup>2</sup>C Timing

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization.

<sup>&</sup>lt;sup>2</sup> Specified at recommended operating conditions

$<sup>^{3}</sup>$  4.7  $k\Omega$  should be added externally.

### 1.10 High Speed Serial Interface Timing Specifications

Typical values: Tc=25 °C, DV $_{\rm DD}$ , ALV $_{\rm DD}$ =1.8 V, AHV $_{\rm DD}$  =3.3 V

Table 1-11. High Speed Serial Interface Timing Specifications

| Parameter                                            | Symbol (refer to figure below) | Min | Тур | Max | Units |

|------------------------------------------------------|--------------------------------|-----|-----|-----|-------|

| Clock Frequency                                      | fclk=1/Tclk                    |     |     | 40  | MHz   |

| Data in to clk hold time                             | Tdh                            | 5   |     |     | ns    |

| Data in to clk set-up time                           | Tds                            | 5   |     |     | ns    |

| Enable to clk set up time                            | Tcs                            | 5   |     |     | ns    |

| Enable to clk hold time                              | Tch                            | 5   |     |     | ns    |

| Read data output valid following rising edge of SCLK | Tdd                            | 2   |     | 9   | ns    |

| SCLK duty cycle                                      |                                | 45  |     | 55  | %     |

| NOTES:  1 Maximum output capacitance o               | f 5 pF.                        | 1   | ı   |     |       |

Figure 1-6. Serial Interface Sequential Write

Figure 1-7. Serial Interface Random Write

Figure 1-8. Serial Interface Sequential Read

Figure 1-9. Serial Interface Random Read

Rev V1

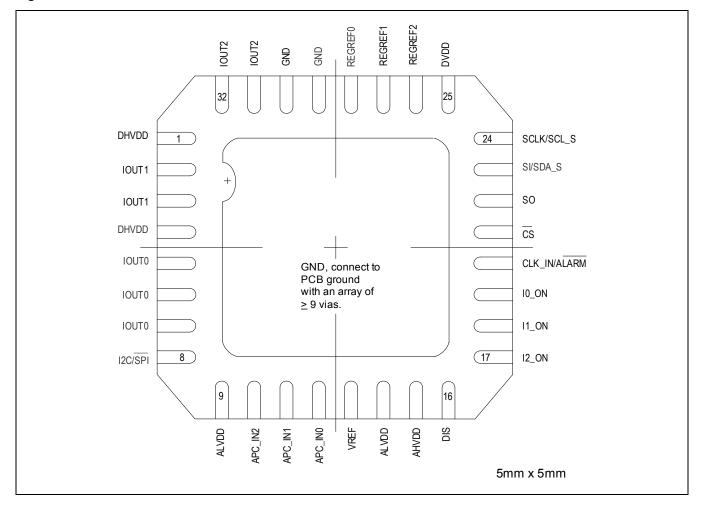

#### 1.11 M08886 Pinout

The M08886 is packaged in a 5x5 mm 32-pin QFN package with 0.5 mm pin pitch.

Figure 1-10. M08886 Pinout

### 1.12 Pin List and Descriptions

Table 1-12. Pin List and Descriptions

| Pin              | Name                           | Туре            | Function                                                       |

|------------------|--------------------------------|-----------------|----------------------------------------------------------------|

| 1 and 4          | DHV <sub>DD</sub>              | Supply          | 3.3 V digital supply                                           |

| 2 and 3          | IOUT1                          | Analog          | 1A LED/Laser driver output                                     |

| 5, 6 and 7       | IOUT0                          | Analog          | 2A LED/Laser driver output                                     |

| 8                | I <sup>2</sup> C/SPI           | CMOS(PD)        | Serial interface select (L=I <sup>2</sup> C,H=SPI)             |

| 9 and 14         | ALV <sub>DD</sub>              | Supply          | 1.8 V analog supply                                            |

| 10               | APC_IN2                        | Analog          | Monitor PD input 2 (assignable)                                |

| 11               | APC_IN1                        | Analog          | Monitor PD input 1 (assignable)                                |

| 12               | APC_IN0                        | Analog          | Monitor PD input 0 (assignable)                                |

| 13               | VREF                           | Analog          | Current reference generator                                    |

| 15               | AHV <sub>DD</sub>              | Supply          | 3.3 V analog supply                                            |

| 16               | DIS                            | CMOS(PU)        | Disable all laser drivers                                      |

| 17               | 12_ON                          | CMOS(PD)        | Turns on driver 2                                              |

| 18               | I1_ON                          | CMOS(PD)        | Turns on driver 1                                              |

| 19               | 10_ON                          | CMOS(PD)        | Turns on driver 0                                              |

| 20               | CLK_IN/ALARM                   | CMOS            | External clock input or alarm output                           |

| 21               | CS                             | Open Drain (PU) | Serial enable                                                  |

| 22               | SO                             | Open Drain (PU) | Serial data out                                                |

| 23               | SI/SDA_S                       | Open Drain (PU) | Serial data in/I <sup>2</sup> C data slave                     |

| 24               | SCLK/SCL_S                     | Open Drain (PU) | Serial clock/I <sup>2</sup> C clock slave                      |

| 25               | DV <sub>DD</sub>               | Supply          | 1.8 V digital supply                                           |

| 26               | REGREF2                        | Analog          | Regulator reference output 2 (assignable)                      |

| 27               | REGREF1                        | Analog          | Regulator reference output 1 (assignable)                      |

| 28               | REGREF0                        | Analog          | Regulator reference output 0 (assignable)                      |

| 29 and 30        | GND                            | Supply          | Ground                                                         |

| 31 and 32        | IOUT2                          | Analog          | 1A driver output                                               |

| center pad       | GND                            | Supply          | Electrical and Thermal Ground (must be connected electrically) |

| NOTE: PD means p | pulled down, PU means pulled u | 0.              |                                                                |

Rev V

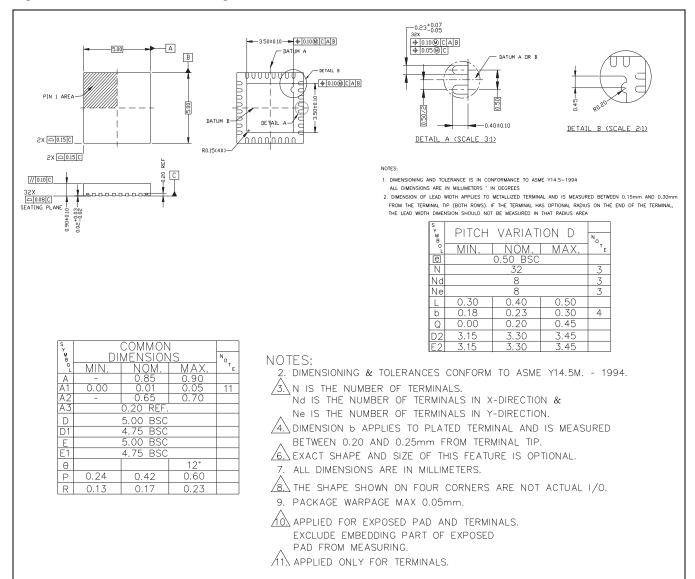

### 1.13 Package Information

Figure 1-11. Sawn QFN32 Package Information

Rev V1

## 2.0 Functional Description

The M08886 is a highly integrated laser/led driver for LCD/LCoS laser/led projection display applications. It provides control and monitoring of up to three LEDs/lasers (typically RGB: red, green and blue) and monitoring and control of temperature and DC-DC converters reference generators for optimal laser/led supply.

The RGB laser/led front end consists of three 12-bit current output digital to analog converters (DACs) and three high efficiency laser drivers with de-speckle technology. The current generated by each DAC is the sum of two components - an offset component (corresponding to the threshold current of the laser, set offset to 0 for LEDs) and a gain component corresponding to the video information.

During projection, the laser/LED current can be controlled by writing the desired current directly to the output DAC or the Laser/LED current can be controlled by an external photodetector. In this case ColorMinder Automatic Power control loop (APC) continually adjusts the gain component of the laser/led current to hold the photodiode current constant during its "on time" and therefore the optical power of the laser/led is held constant at the desired value. The APC will match the photodetector current corresponding to the laser/led turned on at that moment with the current programmed by the video processor for the 13bit target analog to digital converter as the target. The current generated by the target DAC corresponds therefore to the desired optical power level. The APC adjusts the laser/led drive currents in order to maintain the appropriate optical power. The optical power is adjusted every time a color is on during a frame or a portion of it. The threshold current for the lasers (offset portion of the DAC currents) are also automatically adjusted by the APC loop during the blanking period (*IO\_ON, I1\_ON* and *I2\_ON* all low) or they can be programmed by the user.

The M08886 internally monitors the required laser/led driver headroom and sends a control signal to an external DC-DC converters to optimally adjust each laser/led's supply voltage.

The M08886 internal registers are loaded from an external microcontroller through a slave  $I^2C$  interface or a 4-wire high speed interface. The host  $\mu$ controller can monitor and read back the analog to digital converter outputs either though the slave  $I^2C$  or the SPI interface.

#### 2.1 Automatic Power Control (APC)

ColorMinder automatic power control (APC) can keep the laser/led power constant and the color balanced by comparing the monitor photodetector (RGB color sensor) currents to target values programmed into the 13-bit target DACs.

At power-up the APC can be enabled/disabled independently for each channel by setting apc**x**\_ctrl0[2:1]=11. For channels with disabled APC the laser/led currents are controlled through the serial interface using bits iout**x**\_gain[11:0].

It is possible to freeze the APC loop for each channel by using loop\_ctrl[2:0]. In this case the M08886 will stop updating the gain or offset IOUTx currents independently of the state of  $Ix_ON$  pins.

Rev V1

The photodiode (RGB sensor) target values are programmed via the serial interface in registers target2[12:0], target1[12:0] and target0[12:0] respectively for *IOUT2*, *IOUT1* and *IOUT0*. When the corresponding color is turned on as signaled by the transition of *IO\_ON*, *I1\_ON* or *I2\_ON* from low to high the LED/Laser drive currents are automatically adjusted up or down to always make the photodetector current (RGB sensor current) match the target current.

If desired, these target currents can be adjusted on a frame by frame basis to optimize contrast and save battery power depending on the brightness required for a particular frame.

When an *Ix\_ON* signal is enabled (low to high transition) the new APC target is strobed in and the proper incoming monitor photodetector current is selected to control the output current by an analog multiplexer from *APC\_INO*, *APC\_IN1* or *APC\_IN2*. For each output channel the photodetector input corresponding can be selected using apcx\_ctrl0[2:1]. This allows the use of multiple independent photodetectors such as a 3 channel RGB color sensor with color filters optimized for each channel or instead a single broadband (color insensitive) photodetector can be used for all 3 channels. If a single broadband photodetector is used and connected to *APC\_IN0* all the apcx\_ctrl0[2:1] should be set to 00b.

#### 2.1.1 Simple Implementation of APC Control

In addition to the controls described in this section, also see the section below on the TIA.

If the APC targets are not changing frame by frame, a basic register configuration can be used as shown below.

Table 2-1. Basic Register Configuration for APC Control

| Name                                                  | Address                                        | Recommend<br>Setting                | Description                                                                                                                                                                                                  |

|-------------------------------------------------------|------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| loop_ctrl                                             | 0x29h                                          | 00h                                 |                                                                                                                                                                                                              |

| apc0_ctrl0[2:1]<br>apc1_ctrl0[2:1]<br>apc2_ctrl0[2:1] | 0x40h[2:1]<br>0x3Ch[2:1]<br>0x38h[2:1]         | 00000xx0b<br>00000xx0b<br>00000xx0b | Select which photodiode (RGB sensor) input will control which output. Setting depends on hardware connection to photodiode(s) and which channels will use APC control. See Register description for details. |

| targetxith_msb targetxith_lsb                         | 0x2Ch, 0x2Dh,<br>0x30h, 0x31h,<br>0x34h, 0x35h | 00h                                 | Set the laser offset (threshold) at 0. See section on Despeckle for use of laser offset.                                                                                                                     |

| target <b>x</b> _msb                                  | 0x2Ah, 0x2Eh, 0x32h<br>0x2Bh, 0x2Fh, 0x33h     | 000xxxxxb                           | Set the gain target at desired level                                                                                                                                                                         |

| target <b>x</b> _lsb                                  |                                                | xxh                                 |                                                                                                                                                                                                              |

| apc0_ctrl2<br>apc1_ctrl2<br>apc2_ctrl2                | 0x3Eh<br>0x3Ah<br>0x36h                        | 00h                                 | Set the clock step to 0 for controlling the step response of the output                                                                                                                                      |

| apc0_ctrl1<br>apc1_ctrl1<br>apc2_ctrl1                | 0x3Fh<br>0x3Bh<br>0x37h                        | 03h                                 | Clock divide set to 16.                                                                                                                                                                                      |

The APC controller increases or decreases the value of the gain portion of the laser/led *IOUTX* current so the photodetector current will match the gain target current for that channel.

Rev V1

If more than one laser/led is turned on (2 or 3 of *IO\_ON*, *I1\_ON* or *I2\_ON* are high at the same time) the M08886 freezes the update of the APC loop for as long as more then one of the *Ix\_ON* signal is on. This prevents the APC loop from using wrong photodetector information in case a single photodetector is used with no color filter. It should be noted that 2 or more low to high transitions of any of the *I0\_ON*, *I1\_ON* or *I2\_ON* within 200 ns of each other will violate internal timing and will result in unpredictable operation. Care should be taken to prevent damage to the part when multiple laser/leds are enabled. The power dissipation of the part should be kept below the level that will result in a die temperature exceeding 125 °C.

#### 2.1.2 Highly Featured Implementation of APC Control

Table 2-2. Highly Featured Register Configuration for APC Control

| Name                                                  | Address                                        | Recommend<br>Setting                | Description                                                                                                                                                                                                  |

|-------------------------------------------------------|------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| loop_ctrl                                             | 0x29h                                          | 00h                                 | Setting 0x29h[7:5]=111b may be useful for very low EMI applications with slow current slew on the outputs.                                                                                                   |

|                                                       |                                                |                                     | Set 0x29h[3]=1b when using an external clock in PWM or MPG mode.                                                                                                                                             |

| apc0_ctrl0[2:1]<br>apc1_ctrl0[2:1]<br>apc2_ctrl0[2:1] | 0x40h[2:1]<br>0x3Ch[2:1]<br>0x38h[2:1]         | 00000xx0b<br>00000xx0b<br>00000xx0b | Select which photodiode (RGB sensor) input will control which output. Setting depends on hardware connection to photodiode(s) and which channels will use APC control. See Register description for details. |

| targetxith_msb<br>targetxith_lsb                      | 0x2Ch, 0x2Dh,<br>0x30h, 0x31h,<br>0x34h, 0x35h | 00h                                 | Set the laser offset (threshold) at 0. See section on Despeckle for use of laser offset.                                                                                                                     |

| target <b>x</b> _msb                                  | 0x2Ah, 0x2Eh, 0x32h<br>0x2Bh, 0x2Fh, 0x33h     | 000xxxxxb                           | Set the gain target at desired level                                                                                                                                                                         |

| target <b>x</b> _lsb                                  |                                                | xxh                                 |                                                                                                                                                                                                              |

| apc0_ctrl2<br>apc1_ctrl2<br>apc2_ctrl2                | 0x3Eh<br>0x3Ah<br>0x36h                        | A8h                                 | This setting may vary depending on photodiode capacitance, desired risetime and how much overshoot can be tolerated.                                                                                         |

| apc0_ctrl1<br>apc1_ctrl1<br>apc2_ctrl1                | 0x3Fh<br>0x3Bh<br>0x37h                        | 92h                                 | This setting may vary depending on photodiode capacitance, desired risetime and how much overshoot can be tolerated                                                                                          |

One of the reasons to choose a more complicated APC control method is modulation of frame-to-frame illumination. Modulating the output amplitude of the Laser/LED can increase the contrast in an image and it can improve battery life. Changes in the LED/Laser output on a frame-by frame basis requires that the LED/Laser "step" to the new APC target amplitude in a fraction of the frame time. The fast step to a new level requires that some care be taken in the feedback response of the photodetector and LED/Laser.

Other reasons to choose a more complicated APC control method might be slew rate control of the outputs for EMI or DC-DC converter stability reasons. In this case the feedback response does not require as much consideration.

The primary methods for adjusting the feedback response of the photodetector are in registers apcx\_ctrl2,1,0. The TIA response will also need to be compensated as described in the section below.

Rev V1

The digital APC loop is designed to settle to the desired optical output power in 5  $\mu$ s: the optical power measured in the subsequent 5  $\mu$ s should be within +/-1% of the desired value. To achieve optimal settling time, the APC loop must be adjusted to the laser/led/monitor photodetector characteristics.

Each *IOUTX* slew rate is independently controllable in 3 time intervals. The first time interval begins when *Ix\_ON* goes high and the length of the first time interval is defined in apcx\_ctrl2[7:6] and is from 0 to 255 clock cycles. The length of the second time interval is defined in apcx\_ctrl2[5:4] and is from 0 to 127 clock cycles. The length of the third time interval is defined in apcx\_ctrl2[3:2] and is from 0 to 127 clock cycles. There is a fourth time interval which is not definable which is from the end of the third time interval until the time when *Ix\_ON* goes low.

The APC clock is the system clock divided by 3. The PWM and MPG clock is the system clock divided by 16 and may be further divided by register clk\_div[7:0]. The source of the system clock is set in register despeckle\_clk[1:0]. If only LED light sources are used (despeckle for lasers not needed) then power consumption can be minimized by selecting despeckle\_clk[1:0]=11b and osc\_ctrl[3]=1b. If the despeckle feature is used then despeckle\_clk[1:0]=00b and osc\_ctrl[3]=0b and the clock frequency can be tuned at osc\_ctrl[2:0]. The APC clock for each channel may be divided (apcx\_ctrl1[1:0]) and the point at which the clock division begins following *lx\_ON* high (apcx\_ctrl2[1:0]) can also be set. So a clock cycle in an early interval may be different than a clock cycle in a later interval. And the change in clock rate may occur in the middle of an interval. Decimation may also be enabled for any of the APC channels at apcx\_ctrl0[7:5]. If decimation is enabled then the APC loop will not correct the output current until the measured photodiode current doesn't match the target photodiode current several measurements in a row with the same polarity (too high or too low). The number of consecutive measurements required of the same polarity is determined by the decimation factor.

During the first time interval following Ix\_ON high the corresponding IOUTX output current will increase by an amount defined in apcx\_ctrl1[7:6] each clock cycle if the photodetector current is less than the target current set in targetx\_msb and targetx\_lsb and it will decrease by that amount each clock cycle that the photodetector current is less than the target current. Similarly during the second time interval the IOUTX output current will increase/decrease by an amount defined in apcx\_ctrl1[5:4] each clock cycle if the photodetector current is less/greater than the target current. During the third and fourth intervals the step size is always one LSB.

The OUT0 LSB is nominally 488 μA. The OUT1 and OUT2 LSBs are nominally 244 μA.

The overshoot of the *OUTX* output current will be at a maximum during the first time interval where the current step is greatest. It will be proportional to the current defined in apcx\_ctrl1[7:6] and it will also be a function of the loop delay which is approximately 3 clock cycles. Either an over-damped or under-damped response may independently be programmed into the response of the M08886 output channels as desired.

The target DAC has a conversion rate of 30 MSPS and the full scale value is 3 mA with a resolution of 13 bit or 0.366  $\mu$ A. As an example, if the full scale photodetector value is 200  $\mu$ A, the possible selectable power levels are up to 546 decimal (200  $\mu$ A /0.366  $\mu$ A). In this example, full scale will correspond to a target DAC (target**x**[12:0]) value of 111h and no power will correspond to 0h.

#### 2.1.3 Compensating the TIA at the Photodetector Input

The maximum photodetector current supported by the M08886 is 3 mA. Because of the different characteristics of each photodetector/laser/led the user should select the proper analog filter network for each of the channels by programming tia\_ctrl[1:0].

Rev V1

#### 2.1.4 Laser Offset (threshold) Tracking with APC

If lasers are being used instead of LEDs, the M08886 has the capability to automatically adjust offset (laser threshold) as well as gain. In most cases it is sufficient to only use the gain portion of APC control with a laser and the offset controls can be ignored. If the despeckle function is being used, offset tracking is a useful option.

The offset portion of the DAC currents is adjusted during the blanking signal following the period where the laser is on. The blanking period is automatically recognized by the M08886 as the period during which all the colors are off (I0\_ON, I1\_ON and I2\_ON are all low). During that period the target DAC is switched to the user programmed target for the offset current and the M08886 will output and adjust only the offset (laser threshold) portion of the DAC, each of the 3 laser drivers will output only the current corresponding to the threshold (offset DAC current) and the automatic power control loop will adjust the threshold during that period. The offset target for each of the lasers can be programmed using following registers target2\_ith[12:0], target1\_ith[12:0] and target0\_ith[12:0]. The offset target should be chosen low enough as to not interfere with the blanking and high enough to allow meaningful feedback for the APC loop.

The decimation factor for offset control is set in register dec\_off\_ctrl[2:0]. The offset current will not be corrected until multiple occurrences of offset error are detected with the same polarity (too high or too low). The number of consecutive errors required before a correction is made is determined by the decimation factor.

During each blanking period the M08886 current starts from the previously determined and stored laser offset current. The laser driver will be able to track laser threshold variation even for short blanking periods because laser threshold varies slowly (typically based on temperature variation and laser aging). The minimum allowed blanking signal is 200 nsec.

Laser threshold tracking by means of APC can be disabled individually at power-up for each channel using apc**x**\_ctrl0[4] and it is automatically disabled if apc**x**\_ctrl0[2:1]=11b (APC disabled). The threshold current can be programmed in the part for each of the lasers using bits iout**x**\_offset[11:0]. If the programmed offset current does not track (with temperature and laser aging) the actual laser offset, the APC settling might be slowed down or laser power overshoot at turn-on might occur. When the APC for the offset current is disabled the part will automatically output 0 current for all the lasers during blanking.

#### 2.2 LASER/LED Current DACs

The M08886 includes three monotonic digital to analog converters (DACs) which generate the currents for the three laser/leds, the current is converted from a digital code given by the sum of the offset (laser threshold) and gain (video information). The offset and gain values can be either updated via registers or by the APC loop as described in the previous paragraph.

The three laser/led DACs have a range scaled to the laser/led driver output of 0 to 1A for *IOUT1* and *IOUT2* and 0 to 2A for *IOUT0*, a resolution of 12 bits and an update rate of 30 MSPS.

The integrated laser/led drivers deliver the DACs current to the laser/led diodes.

The drivers include MACOM proprietary de-speckle feature which significantly reduces appearance of speckle in laser light by means of high speed modulation of the laser driver current. The de-speckle feature can be simply enabled or disabled via register despeckle\_ctrl[7:0]. With the APC loop enabled, the M08886 automatically adjusts the power level and no other adjustments are required. If open loop is used then laser power calibration must be performed with the de-speckle feature enabled.

Rev V1

Each laser/led driver output (IOUTx) is controlled by the corresponding ON signal (Ix\_ON). Rise/fall time from the laser/led driver is typically 2 ns into a resistive electrical load. The risetime will be dominated by the DC-DC converter settling time in applications where a single DC-DC converter output voltage tracks the optimal LED/laser anode voltage.

To match the significantly slower rise and fall time of the LCD/LCoS the M08886 features a programmable delay which can shift the turn-on of the laser/led once the corresponding ON signal goes to high. The delay is implemented as a programmable 10bit counter that counts clock cycles of the internal clock selected at register 0x28h[1:0] divided by 16. (either 320 MHz or 42 MHz may be selected). If the 320 MHz/16 oscillator is selected then 19.5 MHz clock cycles are counted at the rising edge of each laser/led ON signal (*IO\_ON, I1\_ON* and *I2\_ON*) the counter is decremented and the laser/led is actually turned on only when the counter reaches 0. The laser/led is turned off on the falling edge of the corresponding laser/led ON signal (*IO\_ON, I1\_ON, I2\_ON*). The maximum delay achievable is therefore 52.4 µs if the 320 MHz/16 clock is selected (1023 times the 50 ns period of the 19.5 MHz internal oscillator). Additional delay can be achieved by using the M08886 programmable divider of the internal clock. The internal clock can be divided down by a factor of 1, 2, 4, 16, 256, 512, 1024, and 2048. This can be obtained by writing register clk\_div[7:4]. The values of the programmable counter for the red, green and blue laser/led are stored in bits on\_count2[9:0], on\_count1[9:0], and on\_count0[9:0] respectively. The rising edge of the *Ix\_ON* signals strobe the corresponding on\_countx[9:0] value into the M08886 timing controller therefore if the on\_count register value is changed during the on time for that color the effect of the register change will be available during the next color cycle.

If the on\_countx is programmed to 00 0000 0000b the PWM feature is disabled for IOUTx.

## 2.2.1 Increasing the Maximum LED/Drive Current by Combining Outputs

When multiple channels (2 or 3) of the M8886 inputs and outputs are shorted together to obtain a single higher current channel then set opmode\_ctrl0[5]=1b. The lx\_ON should be shorted together for the channels that are being combined and if they are not shorted their state changes should occur within 10 ns of each other.

It should be pointed out that the M08886 has a single bias generating circuit which is toggled between different output stages depending on the lx\_ON.

The architecture is such that, when multiple outputs are enabled, the biasing is generated from one of them (the one with the lowest channel number) and fed to the other channel. Because of typical circuit fabrication variations and mismatches the current out of a certain channel may therefore vary between the case when the channel is operated independently vs. the case when channel is operated in conjunction with another as when a channel is operated independently the biasing is generated by its own biasing circuit. This does not impact the current stability over supply and temperature of the current generated by each channel.

For example, if channel 0 and channel 1 are shorted at the input and output the biasing for channel 1 is now controlled by channel 0.

### 2.3 Laser\LED Voltage Supply Control

By controlling the Laser\LED anode voltage with the REGREF outputs the M08886 can optimize (minimize) the voltage on the output drive pins to the level that insures accurate current drive levels and minimizes power dissipation. Nominally the outputs need 350 mV of headroom but the M08886 will determine the actual level. An internal amplifier is used to monitor the output stage voltage drop and to compare it against an internal reference

Rev V1

voltage coming from a replica circuit. The output of the amplifier at the REGREF pins will control the feedback input of a DC-DC converter to adjust the output voltage (LED or Laser anode voltage) of the DC-DC converter.

The block diagram below illustrates the use of this feature in the system.

Figure 2-1. laser/led Supply Control Block Diagram

In fact there are three laser/leds and therefore three channels in the REGREF. The following block diagram shows the three channels together.

Figure 2-2. Controlling Laser/LED Supply with Three DC-DC Converters

Rev V1

In case a single DC-DC converter is used, *REGREF0* can be multiplexed automatically between three output values. The following block diagram shows this configuration. The strobe signal for each of the three preprogrammed output of *headroom setting DAC* can be independently programmed to be the falling or raising edge of the *Ix\_ON* signals. This feature allows a single DC-DC converter to be used to generate the supply for all the laser/leds independently of the order of color cycling in the projector system. When the falling edge is selected, one of the two possible color sequence needs to be selected by using opmode\_ctrl1[5].

Figure 2-3. Controlling Laser/LED Supply with Single DC-DC Converter

The M08886 internal circuitry will regulate the voltage at each of the *IOUTx* pins during the operation of the laser/led to a voltage equal to the required headroom of the laser/led driver in the actual operating condition by mean of adjusting the external DC-DC converter feedback point or reference voltage.

The replica circuit can be programmed to be a fixed 250 mV instead of the actual replica voltage, using out\_ctrlx [7].

It should be noticed that the laser/led drop will depend on the intrinsic drop across the laser/leds (Vth) plus any drop caused by the series resistance, this includes the laser/led series resistance plus routing resistance on board and in the laser/led package, therefore the voltage drop across the laser/led needs to be adjusted under actual load conditions. This can be done for each *IOUTx* through bits out\_ctrlx [6:4] regardless of the fact that the actual replica is used or the 250 mV fixed voltage.

To guarantee proper operation of the laser/led driver the loop controlling the laser/led supply should be faster then the required APC settling time. The overall supply control loop includes the M08886 and the DC-DC converter. The M08886 supply control path has a first pole at 30 MHz assuming a 5 pF load which should allow the loop to be stable assuming the DC-DC converter has a response time of tens of µs or faster. The load on *REGREFx* pins has a major effect on the internal circuitry of the part and care should be taken to minimize the loading and noise injection at this pin. For added flexibility and to help stability for different DC-DC converters, the gain of the difference amplifier can be programmed for each channel by means of regrefx ctrl[4:2].

In case a single DC-DC converter is used, *REGREF0* can be multiplexed automatically between three output values. The strobe signal for each of the three pre-programmed output of *headroom setting DAC* can be independently programmed to be the falling or raising edge of the *Ix\_ON* signals. This feature allows a single DC-

Rev V1

DC converter to be used to generate the supply for all the laser/leds independently of the order of color cycling in the projector system. When the falling edge is selected, one of the two possible color sequence needs to be selected by using opmode\_ctrl1[5].

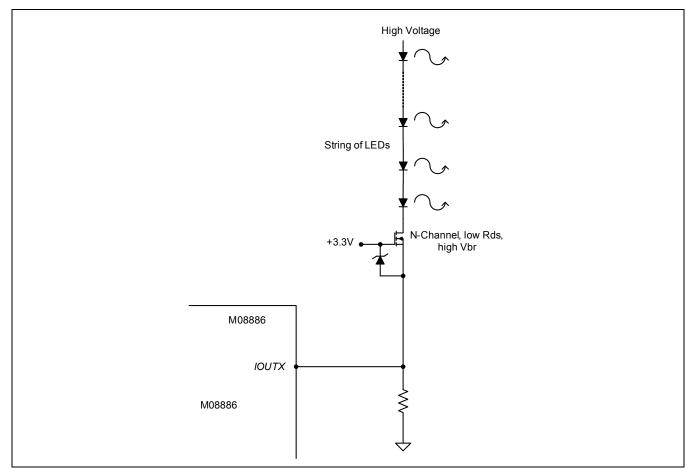

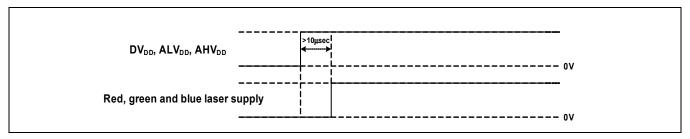

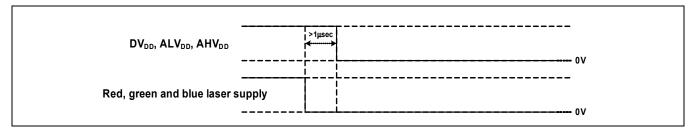

In order to protect the high speed circuitry of the laser/led driver from the high voltage supply at the anodes of the laser/leds, it is imperative that a small quantity of current flow through the laser/led so that the laser/led forward voltage lowers the voltage at the M08886 output pin. The voltage at the laser/led driver output should never exceed 3.63 V therefore an external resistor should be added between the laser/led cathode and ground. The value of the resistor should be chosen so the current flowing is enough to create a sufficient voltage drop on the laser/led. The APC loop will automatically compensate for this "off" current. If the APC loop is disabled and the M08886 is operated open loop this current should be accounted for when programming the desired currents in the system calibration phase. When a single DC-DC converter is used, care should be taken to guarantee that the voltage drop across the red and green laser/led is such that, when the supply is regulated for operation with the highest voltage laser/led, the voltage at all driver pins never exceeds 3.63 V.

Alternative methods to protect the output pins might include a schottky diode to the 3.3 V supply or very low voltage zener.

### 2.4 Pulse Width Modulation (PWM)

The high divider ratios of the internal clock divider (256, 512, 1024, 2048) in conjunction with the programmable counter can be used to decrease the amount of time each laser is on. The optical power can then be controlled by modulating the pulse width of each color pulse. This can yield substantial power savings in laser applications.

The internal ring oscillator varies by +/-15% over parts, temperature and supply and this can directly translate into color intensity variation. The M08886 features a clock input where a high precision clock can be fed to the part and used for this power saving feature. A common 19.44 MHz crystal oscillator or a resonator can be used for this purpose or any high precision clock already available in the system. The precision of PWM power control is directly proportional to the clock accuracy. The PWM block is designed to operate with a maximum frequency of 25 MHz. If CLK\_IN is higher then 25 MHz then the CLK\_IN divider should be enabled and set to 2 or 4 at register clk\_ctrl[2:1] to appropriately scale the frequency. A maximum external clock of 100 MHz is allowed but the internal PWM block can operate at a maximum speed of 25 MHz. External clocks of less than 19.44 MHz are also allowed. The PWM generator then will work at the speed of the *CLK\_IN* (assuming no divider is enabled). The external clock can be selected with register loop\_ctrl[3].

Table 2-3. Clock Selection for PWM and MPG

|            | Register Setting | Description                                                                  |

|------------|------------------|------------------------------------------------------------------------------|

| Laser Mode | 0x28h[1:0]=00b   | 320 MHz system clock selected. PWM and MPG clock is this clock divided by 16 |

| LED Mode   | 0x28h[1:0]=11b   | 42 MHz system clock selected PWM and MPG clock is this clock divided by 16   |

### 2.5 Multi Pulse Generator (MPG)

The M08886 allows for the drive of any of the laser/leds by means of multiple pulses. The multi-pulse generator (MPG) operates in a manner similar to the PWM generator. For each of the laser/leds, two 10-bit counters specify the number of internal clock cycles during which the laser/led associated with them is kept on (gain plus offset

Rev V1

current) and off (0 current). Similar to the PWM block, the MPG block can also use an external clock signal (CLK\_IN).

Assuming the 320 MHz/16 internal oscillator is used, the duty cycle of the pulsed waveform can be controlled with a resolution of one 19.5 MHz clock period or 51.28 ns. If both counters are loaded with the maximum value (1023) the signal driving the laser/led will be a square wave of period 102  $\mu$ s (9.775 kHz). If an external clock is supplied the maximum resolution achievable is 40 ns (25 MHz clock).

The MPG clock can be divided by a factor of 1, 2, 4, 16, 256, 512, 1024, and 2048. This can be obtained by writing register clk\_div[3:0]. Register clk\_div[3:0] is independent of the divider ratio used in the PWM mode (clk\_div[7:4]).

In general the maximum obtainable period for the multi-pulse waveform is 2046 times the clock period (2 times 1023 times the clock period), in this case the duty cycle of the multi-pulse waveform will be 50%.

Because of the 10-bit counter, the duty cycle resolution obtainable is 1/1023 or better then 0.1% assuming the highest count value is used for one of the counters. The duty cycle control resolution is inversely proportional to the maximum counter value.

The control for the *IOUT0*, *IOUT1*, *IOUT2* laser/led on pulses are programmed respectively in the following registers: pulse\_on2[9:0], pulse\_on1[9:0] and pulse\_on0[9:0].

The rising edge of the  $Ix_ON$  signals strobe the corresponding pulse\_on/offx[9:0] values into the M08886 timing controller. If the pulse\_on/pulse\_off register value is changed during the on time for that color the effect of the register change will not occur until the next rising edge of that  $Ix_ON$ .

If the pulse\_on or pulse\_off for a channel is programmed to 000h then the MPG function is disabled for that channel.

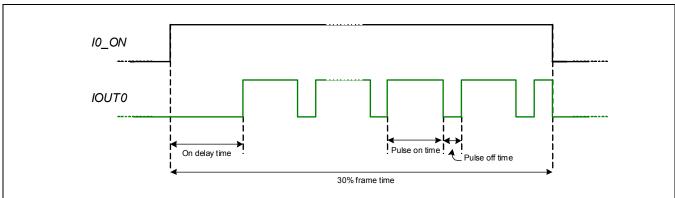

The MPG function is independent of the PWM function: the "On delay time" (PWM function), the "Pulse on time" and "Pulse off time" (MPG functions) can be programmed independently. Also the clock divider for the "On delay time" the "Pulse on/off time" can be selected independently allowing flexibility in defining the driving signals. This is illustrated by the following diagram, where an example for the green laser assigned to channel 0 is represented: the green on signal (*IO\_ON*) and laser current output (*IOUTO*) are drawn.

Rev V1

#### 2.6 Power Save Features

Both the APC and the PWM features can be used to obtain significant system power savings.

The capability of M08886 APC to adjust the laser/led outputs frame by frame allows for significant power savings compared to leaving the laser/leds on all the time at full power. If frame by frame APC is used, then the external µcontroller will store a new 2 byte value in the target DAC for the next power level for each color power that is changing prior to displaying the new frame.

PWM mode also leads to significant power reduction versus standard amplitude modulation. With PWM mode before the display of every new frame the external µcontroller should specify for each color the delay required for pulse width modulation by programming the counter of each color. This can be done by writing four 8-bit registers.

Both power saving methods can be used simultaneously (on different color sources) to obtain the maximum power savings and control over color content of each frame.

The MPG block can also be used as a power saving feature where the color intensity is modulated by varying the duty cycle of the pulsed waveform. In this case the pulse\_on/off registers for every laser need to be programmed to the value corresponding to that frame for a total of eight 8-bit register writes for each new frame. When using MPG with duty cycle modulation for power save mode, accurate power control can be achieved without the use of external clock because internal oscillator variations affect both the on and off period hence the ratio between on/off time remains constant. However, if a very limited number of multiple pulses are used during a frame the internal oscillator variations might impact laser power accuracy.

### 2.7 Safety

A disable pin (*DIS*) is available on the M08886. It disconnects the laser/LED path to ground within 1  $\mu$ s of a low to high transition of *DIS* the laser/led driver current is reduced to 1/10<sup>th</sup> of its starting value.

A register alarm is also available: the safety monitor block compares the output current of each laser/led with 3 thresholds (one for each of the laser/leds) and an alarm is issued if the current is higher than the programmed threshold for any of the lasers/LEDs. The digital thresholds can be programmed in the following registers: alarm\_thx[7:0], these values will be compared to the MSB of the output current.

If CLK\_IN is not being used by MPG or PWM then the pin can be used as an alarm output and external circuitry can be used to shut down power to the laser/leds. Or the alarm status may be read back from register alarm[7:0]. Register Alarm[7:0] is not self clearing: once an alarm has occurred, it must be cleared by the user by writing a 1 to strbalrm\_ctrl[0].

The M08886 can also be programmed (opmode\_ctrl1[3]) to automatically disable the laser/LED outputs when the drive current exceeds the programmed threshold. In this case the laser/led current for that particular laser/led is automatically forced to 0. This feature can be disabled via registers.

The ALARM pin is an open collector output and can operate in status mode or interrupt mode. This can be selected at register opmode\_ctrl0[3]. In status mode the alarm is provided directly to the pin and the pin will be asserted as long as the alarm is present. In some cases the alarm may only be present for only one clock cycle of the internal high speed clock. If the external load on ALARM pin is excessive the alarm signal may not appear at the output because one clock cycle is only 10 ns (100 MHz clock). In interrupt mode the M08886 will issue a positive going pulse on the alarm pin every time the internal alarm changes state. The width of the alarm pulse can be programmed at register opmode\_ctrl0[3:0].

Rev V1

The output stage can also be disabled by the user at register opmode ctrl1[1:0].

#### 2.8 Programmable Serial Interface

The M08886 can be configured to use a 4-wire high speed serial interface or I<sup>2</sup>C. This can be achieved by connecting pin SerSel high or low respectively.

When the part is configured to use I $^2$ C an external host  $\mu$ Controller can access the register and read-back ADC codes from the slave I $^2$ C ( $SDA\_S/SCL\_S$ ). The maximum SCL $\_S$  clock rate is 3.4 MHz. 4.7 k $\Omega$  pull up resistors should be used at  $SDA\_S/SCL\_S$ . These pins are referenced to 1.8 V inside the M08886 but it is OK to connect the pull-up resistors to voltages as high as 2.5 V.

The I<sup>2</sup>C slave address of the M08886 is fixed at 9Ch/9Dh.

The 4-wire high speed interface (SCLC/SI/SO/CS) supports 40 MHz serial clock speeds.

# 2.9 Driving a String of LEDs from a High Voltage Supply