# XRT75L06D

### SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER

APRIL 2005 REV. 1.0.

#### GENERAL DESCRIPTION

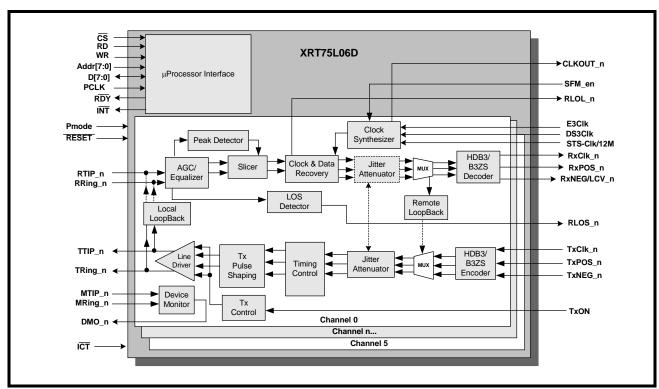

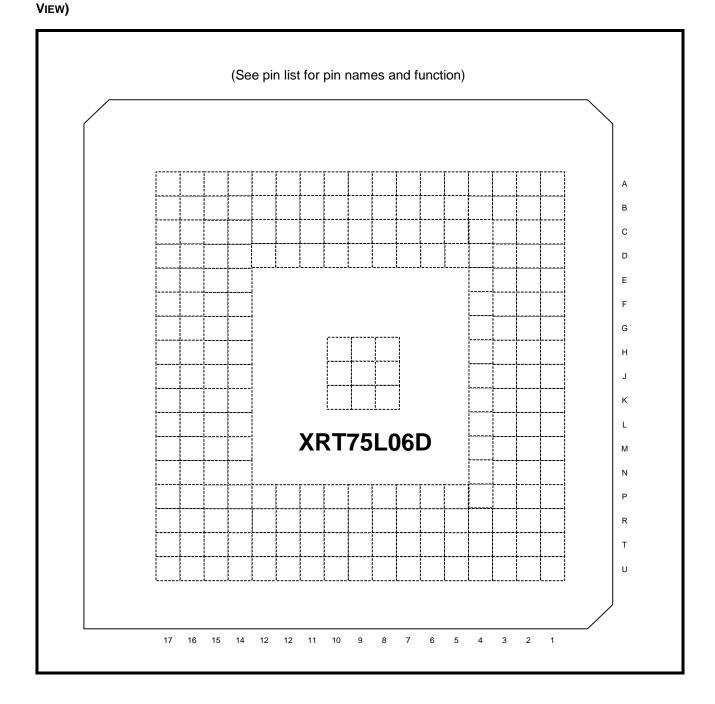

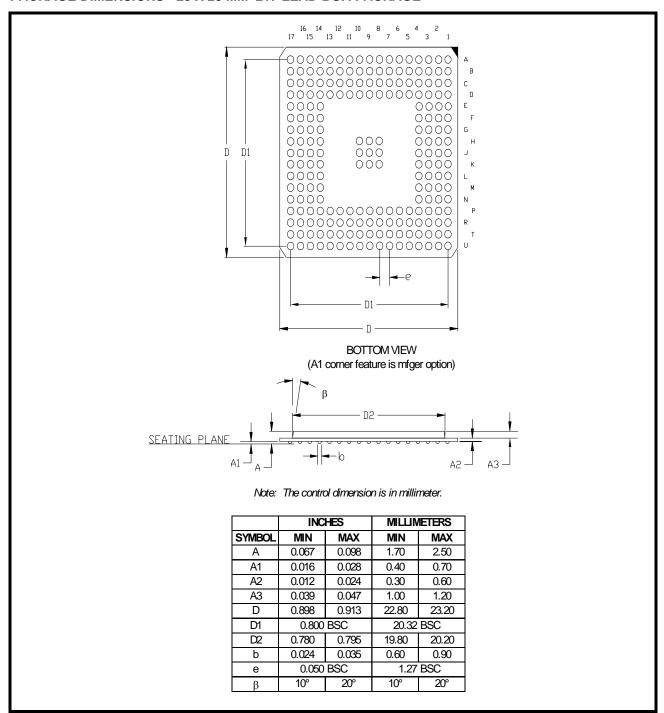

The XRT75L06D is a six channel fully integrated Line Interface Unit (LIU) for E3/DS3/STS-1 applications. The LIU incorporates 6 independent Receivers, Transmitters and Jitter Attenuators in a single 217 Lead BGA package.

Each channel of the XRT75L06D can be independently configured to operate in E3 (34.368 MHz), DS3 (44.736 MHz) or STS-1 (51.84 MHz). Each transmitter can be turned off and tri-stated for redundancy support or for conserving power.

The XRT75L06D's differential receiver provides high noise interference margin and is able to receive data over 1000 feet of cable or with up to 12 dB of cable attenuation.

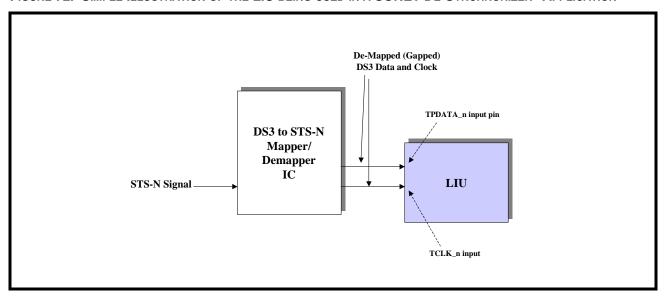

The XRT75L06D incorporates an advanced crystalless jitter attenuator per channel that can be selected either in the transmit or receive path. The jitter attenuator performance meets the ETSI TBR-24 and Bellcore GR-499 specifications. Also, the jitter

attenuators can be used for clock smoothing in SONET STS-1 to DS-3 de-mapping.

The XRT75L06D provides a Parallel Microprocessor Interface for programming and control.

The XRT75L06D supports analog, remote and digital loop-backs. The device also has a built-in Pseudo Random Binary Sequence (PRBS) generator and detector with the ability to insert and detect single bit error for diagnostic purposes.

#### **APPLICATIONS**

- E3/DS3 Access Equipment

- DSLAMs

- Digital Cross Connect Systems

- CSU/DSU Equipment

- Routers

- Fiber Optic Terminals

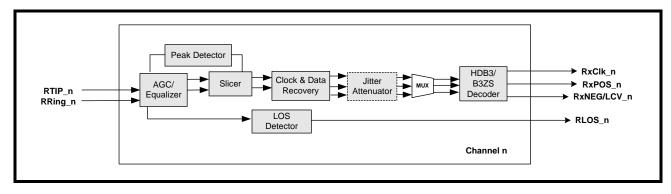

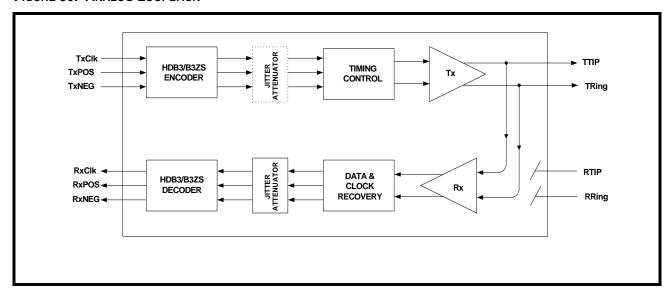

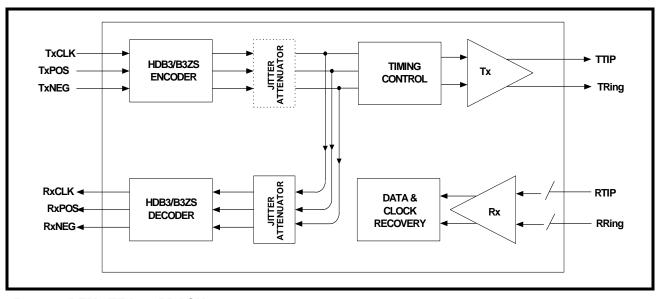

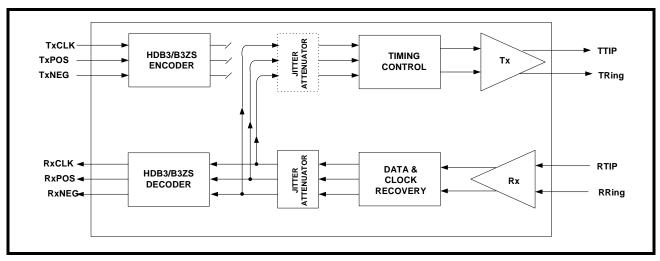

FIGURE 1. BLOCK DIAGRAM OF THE XRT 75L06D

### ORDERING INFORMATION

| PART NUMBER | PACKAGE      | OPERATING TEMPERATURE RANGE |

|-------------|--------------|-----------------------------|

| XRT75L06DIB | 217 Lead BGA | -40°C to +85°C              |

## **EXAF**

#### **FEATURES**

#### **RECEIVER**

- On chip Clock and Data Recovery circuit for high input jitter tolerance

- Meets E3/DS3/STS-1 Jitter Tolerance Requirement

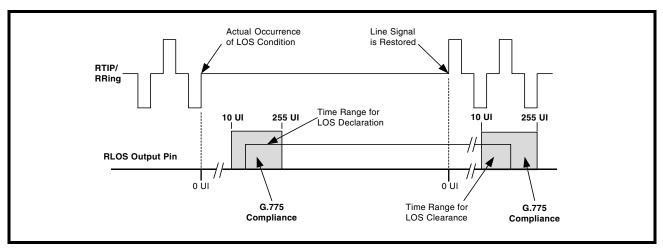

- Detects and Clears LOS as per G.775

- Receiver Monitor mode handles up to 20 dB flat loss with 6 dB cable attenuation

- On chip B3ZS/HDB3 encoder and decoder that can be either enabled or disabled

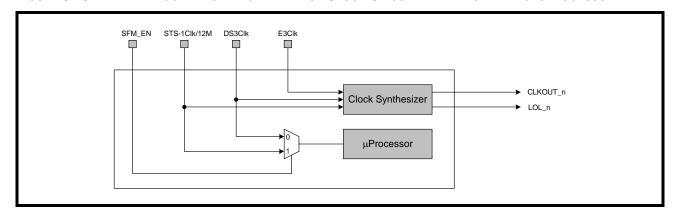

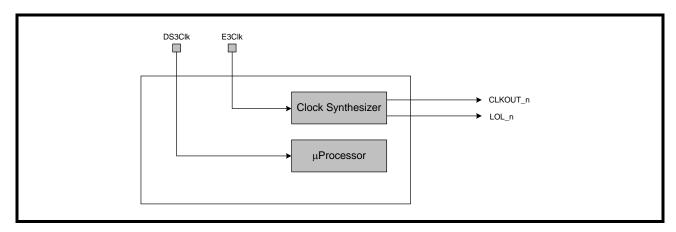

- On-chip clock synthesizer provides the appropriate rate clock from a single 12.288 MHz Clock

- Provides low jitter output clock

#### **TRANSMITTER**

- Compliant with Bellcore GR-499, GR-253 and ANSI T1.102 Specification for transmit pulse

- Tri-state Transmit output capability for redundancy applications

- Each Transmitter can be turned on or off

#### JITTER ATTENUATOR

- On chip advanced crystal-less Jitter Attenuator for each channel

- Jitter Attenuator can be selected in Receive, Transmit path, or disabled

- Meets ETSI TBR 24 Jitter Transfer Requirements

- Compliant with jitter transfer template outlined in ITU G.751, G.752, G.755 and GR-499-CORE,1995 standards

- 16 or 32 bits selectable FIFO size

#### **CONTROL AND DIAGNOSTICS**

- Parallel Microprocessor Interface for control and configuration

- Supports optional internal Transmit driver monitoring

- Each channel supports Analog, Remote and Digital Loop-backs

- Single 3.3 V ± 5% power supply

- 5 V Tolerant digital inputs

- Available in 217 pin BGA Package

- 40°C to 85°C Industrial Temperature Range

#### TRANSMIT INTERFACE CHARACTERISTICS

- Accepts either Single-Rail or Dual-Rail data from Terminal Equipment and generates a bipolar signal to the line

- Integrated Pulse Shaping Circuit

- Built-in B3ZS/HDB3 Encoder (which can be disabled)

- Accepts Transmit Clock with duty cycle of 30%-70%

- Generates pulses that comply with the ITU-T G.703 pulse template for E3 applications

- Generates pulses that comply with the DSX-3 pulse template, as specified in Bellcore GR-499-CORE and ANSI T1.102\_1993

- Generates pulses that comply with the STSX-1 pulse template, as specified in Bellcore GR-253-CORE

- Transmitter can be turned off in order to support redundancy designs

#### RECEIVE INTERFACE CHARACTERISTICS

- Integrated Adaptive Receive Equalization (optional) for optimal Clock and Data Recovery

- Declares and Clears the LOS defect per ITU-T G.775 requirements for E3 and DS3 applications

- Meets Jitter Tolerance Requirements, as specified in ITU-T G.823\_1993 for E3 Applications

- Meets Jitter Tolerance Requirements, as specified in Bellcore GR-499-CORE for DS3 Applications

- Declares Loss of Lock (LOL) Alarm

- Built-in B3ZS/HDB3 Decoder (which can be disabled)

- Recovered Data can be muted while the LOS Condition is declared

- Outputs either Single-Rail or Dual-Rail data to the Terminal Equipment

### REV. 1.0.4

### **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                                                                                        |    |

|------------------------------------------------------------------------------------------------------------|----|

| APPLICATIONS                                                                                               |    |

| FIGURE 1. BLOCK DIAGRAM OF THE XRT 75L06D                                                                  |    |

| ORDERING INFORMATION                                                                                       |    |

| FEATURES                                                                                                   |    |

| Transmit Interface Characteristics                                                                         |    |

| RECEIVE INTERFACE CHARACTERISTICS                                                                          |    |

| FIGURE 2. XRT75L06D IN BGA PACKAGE (BOTTOM VIEW)                                                           |    |

| TABLE OF CONTENTS                                                                                          | 1  |

| PIN DESCRIPTIONS (BY FUNCTION)                                                                             | 4  |

| Transmit Interface                                                                                         |    |

| Receive Interface                                                                                          |    |

| CLOCK INTERFACE                                                                                            |    |

| CONTROL AND ALARM INTERFACE                                                                                |    |

| Analog Power and Ground                                                                                    |    |

| DIGITAL POWER AND GROUND                                                                                   |    |

| 1.0 CLOCK SYNTHESIZER                                                                                      |    |

| FIGURE 3. SIMPLIFIED BLOCK DIAGRAM OF THE INPUT CLOCK CIRCUITRY DRIVING THE MICROPROCESSOR                 |    |

| 1.1 CLOCK DISTRIBUTION                                                                                     |    |

| Figure 4. Clock Distribution Congifured in E3 Mode Without Using SFM                                       | 16 |

| 2.0 THE RECEIVER SECTION                                                                                   |    |

| FIGURE 5. RECEIVE PATH BLOCK DIAGRAM                                                                       |    |

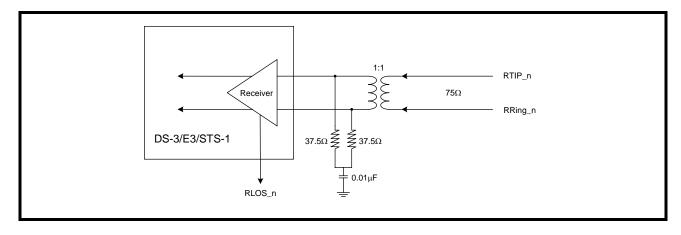

| 2.1 RECEIVE LINE INTERFACE                                                                                 |    |

| Figure 6. Receive Line InterfaceConnection                                                                 |    |

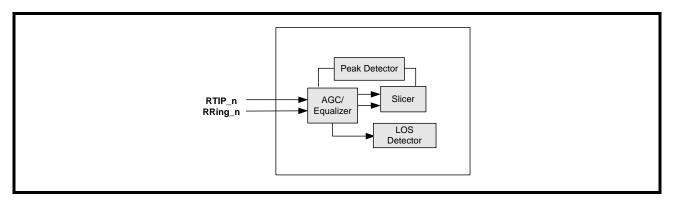

| 2.2 ADAPTIVE GAIN CONTROL (AGC)                                                                            |    |

| 2.3 RECEIVE EQUALIZER                                                                                      |    |

| FIGURE 7. ACG/EQUALIZER BLOOK DIAGRAM                                                                      | 18 |

| 2.4 CLOCK AND DATA RECOVERY                                                                                |    |

| 2.4.1 DATA/CLOCK RECOVERY MODE                                                                             | 18 |

| 2.4.2 TRAINING MODE                                                                                        | 18 |

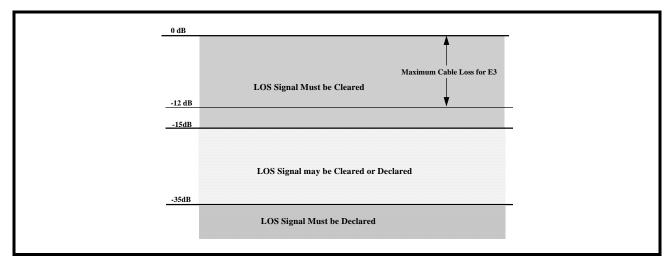

| 2.5 LOS (LOSS OF SIGNAL) DETECTOR                                                                          | 19 |

| 2.5.1 DS3/STS-1 LOS CONDITION                                                                              | 19 |

| TABLE 1: THE ALOS (ANALOG LOS) DECLARATION AND CLEARANCE THRESHOLDS FOR A GIVEN SETTING OF LOSTHR AND REQE |    |

| AND STS-1 APPLICATIONS)                                                                                    |    |

| 2.5.3 E3 LOS CONDITION:                                                                                    |    |

| Figure 8. Loss Of Signal Definition for E3 as per ITU-T G.775                                              | 20 |

| FIGURE 9. LOSS OF SIGNAL DEFINITION FOR E3 AS PER ITU-T G.775.                                             | 20 |

| 2.5.4 INTERFERENCE TOLERANCE                                                                               |    |

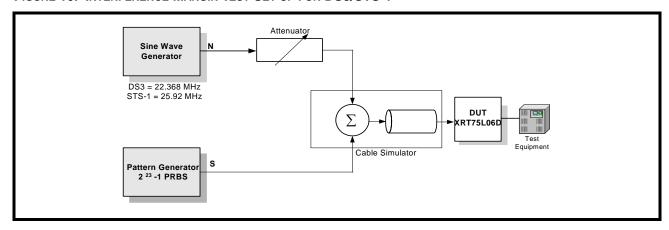

| FIGURE 10. INTERFERENCE MARGIN TEST SET UP FOR DS3/STS-1                                                   |    |

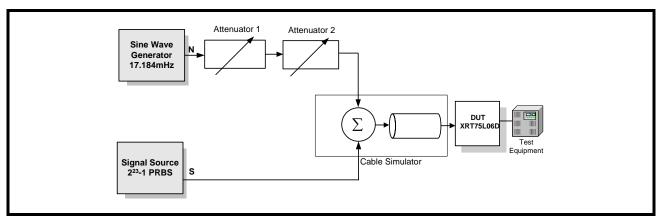

| FIGURE 11. INTERFERENCE MARGIN TEST SET UP FOR E3                                                          |    |

| 2.5.5 MUTING THE RECOVERED DATA WITH LOS CONDITION:                                                        |    |

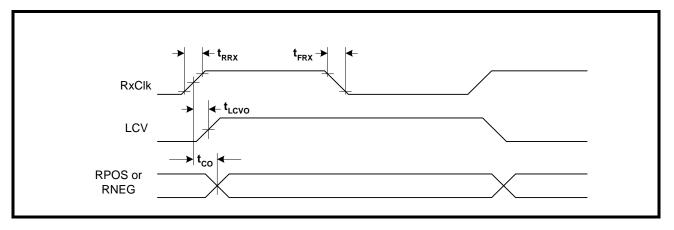

| FIGURE 12. RECEIVER DATA OUTPUT AND CODE VIOLATION TIMING                                                  |    |

| 2.6 B3ZS/HDB3 DECODER                                                                                      | 23 |

| 3.0 THE TRANSMITTER SECTION                                                                                | 24 |

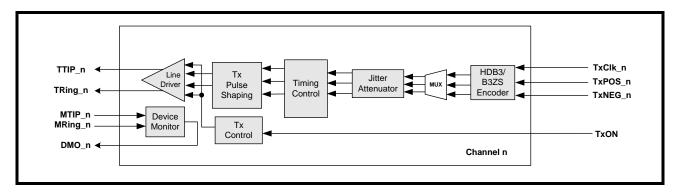

| FIGURE 13. TRANSMIT PATH BLOCK DIAGRAM                                                                     |    |

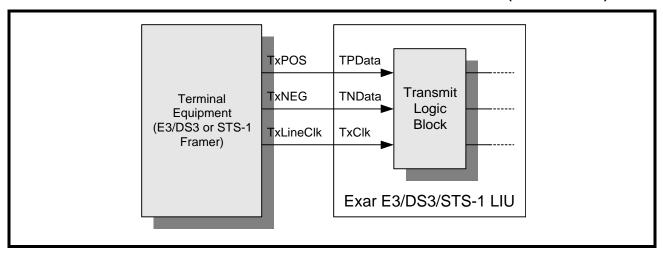

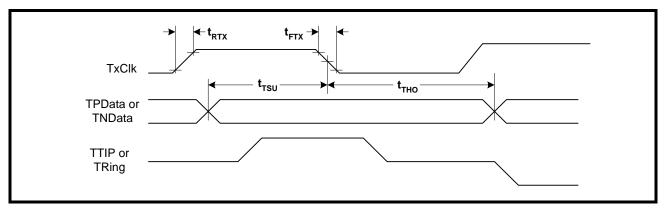

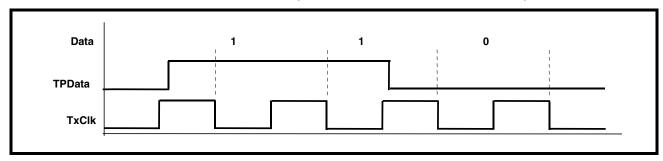

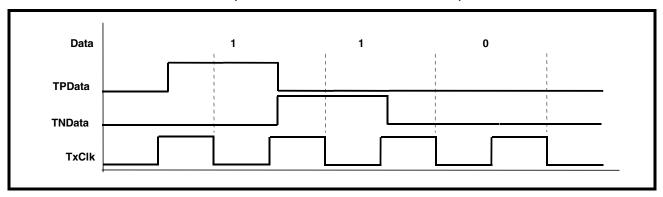

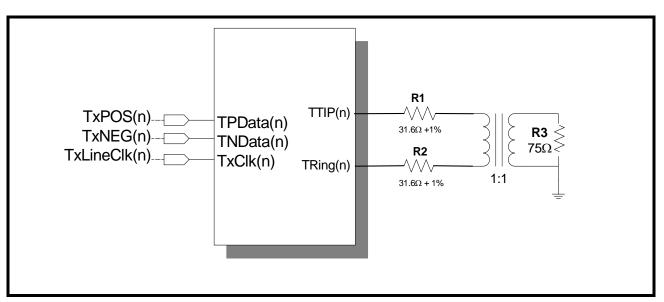

| 3.1 TRANSMIT DIGITAL INPUT INTERFACE                                                                       |    |

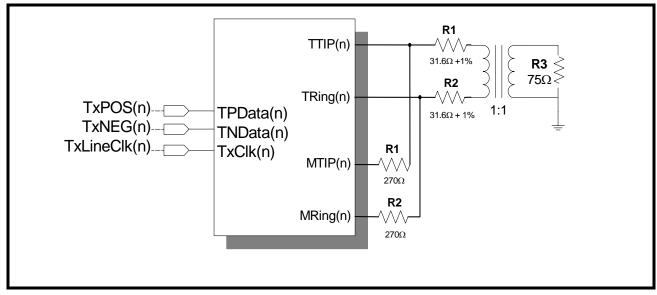

| FIGURE 14. TYPICAL INTERFACE BETWEEN TERMINAL EQUIPMENT AND THE XRT75L06D (DUAL-RAIL DATA)                 |    |

| FIGURE 15. TRANSMITTER TERMINAL INPUT TIMING                                                               |    |

| FIGURE 16. SINGLE-RAIL OR NRZ DATA FORMAT (ENCODER AND DECODER ARE ENABLED)                                |    |

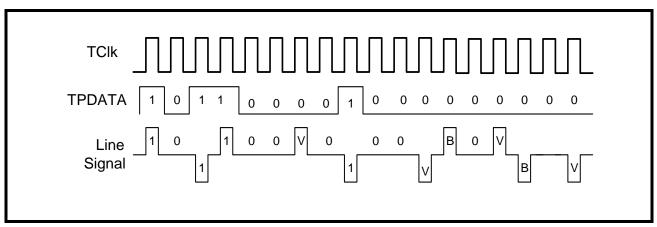

| 3.3 B3ZS/HDB3 ENCODER                                                                                      |    |

| 3.3.1 B3ZS ENCODING                                                                                        | _  |

| FIGURE 18. B3ZS ENCODING FORMAT                                                                            |    |

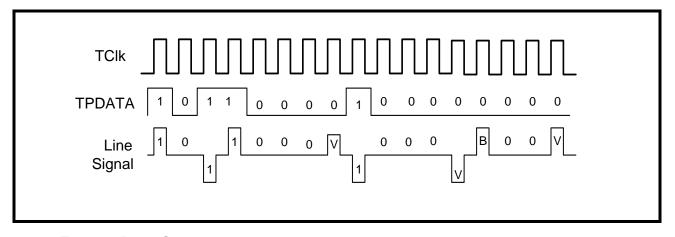

| 3.3.2 HDB3 ENCODING                                                                                        |    |

| FIGURE 17. DUAL-RAIL DATA FORMAT (ENCODER AND DECODER ARE DISABLED)                                        |    |

| FIGURE 19. HDB3 ENCODING FORMAT                                                                            | 27 |

| 3     | 3.4 TRANSMIT PULSE SHAPER                                                                                        |      |

|-------|------------------------------------------------------------------------------------------------------------------|------|

|       | FIGURE 20. TRANSMIT PULSE SHAPE TEST CIRCUIT                                                                     | 27   |

|       | 3.4.1 GUIDELINES FOR USING TRANSMIT BUILD OUT CIRCUIT                                                            | 27   |

| 3     | 3.5 E3 LINE SIDE PARAMETERS                                                                                      | 28   |

|       | FIGURE 21. PULSE MASK FOR E3 (34.368 MBITS/S) INTERFACE AS PER ITU-T G.703                                       | 28   |

|       | TABLE 3: E3 TRANSMITTER LINE SIDE OUTPUT AND RECEIVER LINE SIDE INPUT SPECIFICATIONS                             | . 29 |

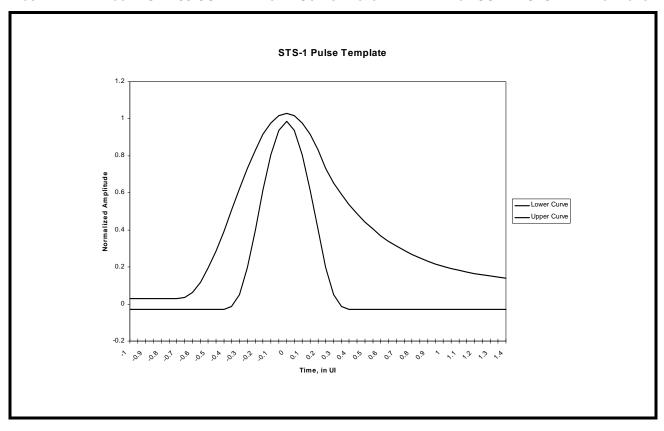

|       | FIGURE 22. BELLCORE GR-253 CORE TRANSMIT OUTPUT PULSE TEMPLATE FOR SONET STS-1 APPLICATIONS                      |      |

|       | TABLE 4: STS-1 PULSE MASK EQUATIONS                                                                              | . 30 |

|       | TABLE 5: STS-1 TRANSMITTER LINE SIDE OUTPUT AND RECEIVER LINE SIDE INPUT SPECIFICATIONS (GR-253)                 | . 31 |

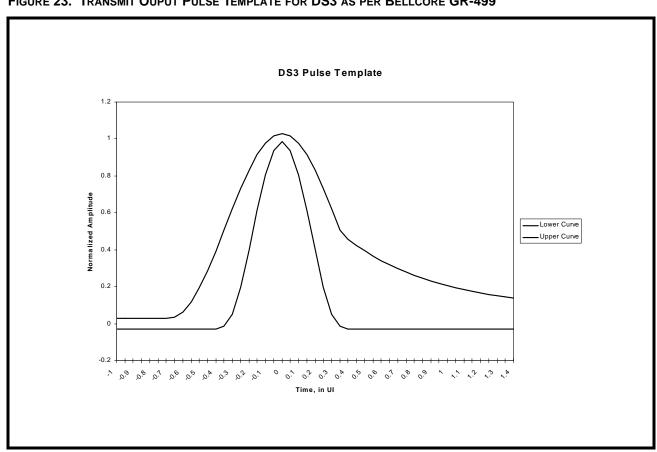

|       | FIGURE 23. TRANSMIT OUPUT PULSE TEMPLATE FOR DS3 AS PER BELLCORE GR-499                                          |      |

|       | TABLE 6: DS3 PULSE MASK EQUATIONS                                                                                |      |

|       | TABLE 7: DS3 TRANSMITTER LINE SIDE OUTPUT AND RECEIVER LINE SIDE INPUT SPECIFICATIONS (GR-499)                   | . 32 |

|       | B.6 TRANSMIT DRIVE MONITOR                                                                                       |      |

|       | Figure 24. Transmit Driver Monitor set-up.                                                                       |      |

| 3     | B.7 TRANSMITTER SECTION ON/OFF                                                                                   |      |

|       | ITTER                                                                                                            |      |

|       |                                                                                                                  |      |

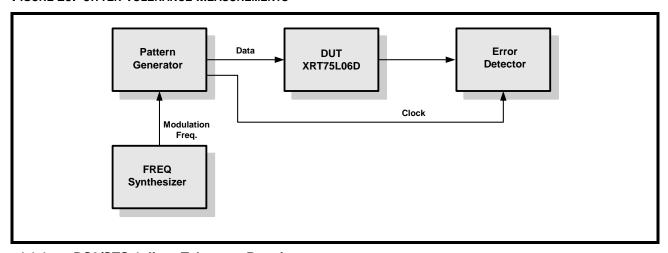

| 4     | 1.1 JITTER TOLERANCE                                                                                             |      |

|       | FIGURE 25. JITTER TOLERANCE MEASUREMENTS                                                                         |      |

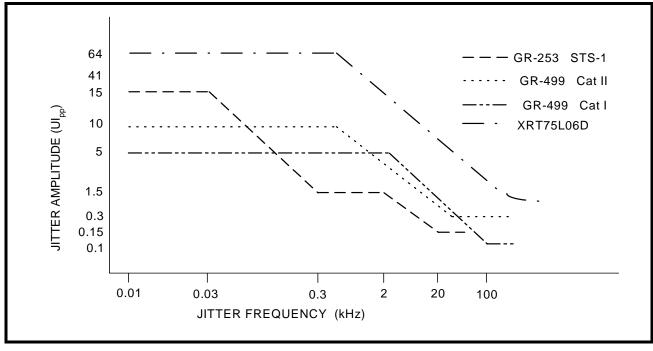

|       | 4.1.1 DS3/STS-1 JITTER TOLERANCE REQUIREMENTS                                                                    |      |

|       | FIGURE 26. INPUT JITTER TOLERANCE FOR DS3/STS-1                                                                  |      |

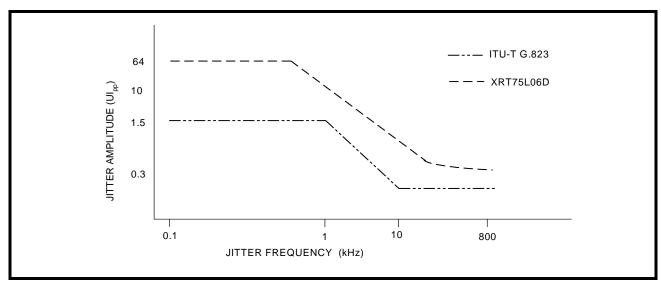

|       | 4.1.2 E3 JITTER TOLERANCE REQUIREMENTS                                                                           |      |

|       | FIGURE 27. INPUT JITTER TOLERANCE FOR E3                                                                         |      |

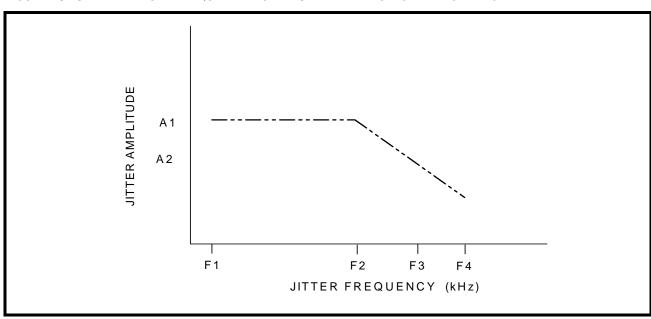

|       | TABLE 8: JITTER AMPLITUDE VERSUS MODULATION FREQUENCY (JITTER TOLERANCE)                                         |      |

| 4     | 1.2 JITTER TRANSFER                                                                                              |      |

|       | TABLE 9: JITTER TRANSFER SPECIFICATION/REFERENCES                                                                |      |

| 4     | 1.3 JITTER ATTENUATOR                                                                                            | 36   |

|       | TABLE 10: JITTER TRANSFER PASS MASKS                                                                             | . 37 |

|       | FIGURE 28. JITTER TRANSFER REQUIREMENTS AND JITTER ATTENUATOR PERFORMANCE                                        | 37   |

|       | 4.3.1 JITTER GENERATION                                                                                          | 37   |

| 5.0 E | DIAGNOSTIC FEATURES                                                                                              |      |

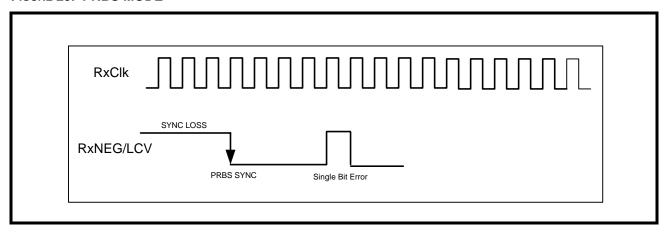

|       | 5.1 PRBS GENERATOR AND DETECTOR                                                                                  |      |

| •     | FIGURE 29. PRBS MODE                                                                                             |      |

|       |                                                                                                                  |      |

| •     | 5.2 LOOPBACKS                                                                                                    |      |

|       | 5.2.1 ANALOG LOOPBACK                                                                                            |      |

|       | FIGURE 30. ANALOG LOOPBACK                                                                                       |      |

|       | 5.2.2 DIGITAL LOOPBACK                                                                                           |      |

|       | FIGURE 31. DIGITAL LOOPBACK                                                                                      |      |

|       | 5.2.3 REMOTE LOOPBACK                                                                                            | -    |

|       | FIGURE 32. REMOTE LOOPBACK                                                                                       |      |

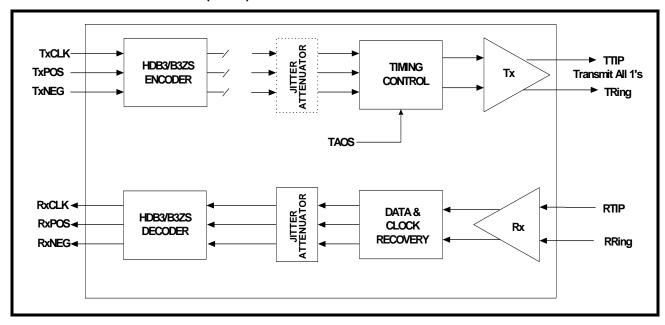

|       | 5.3 TRANSMIT ALL ONES (TAOS)                                                                                     |      |

|       | FIGURE 33. TRANSMIT ALL ONES (TAOS)                                                                              |      |

| 6.0 N | MICROPROCESSOR INTERFACE BLOCK                                                                                   |      |

|       | TABLE 11: SELECTING THE MICROPROCESSOR INTERFACE MODE                                                            | . 42 |

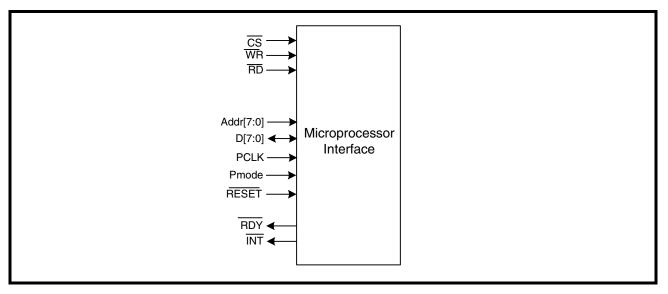

|       | FIGURE 34. SIMPLIFIED BLOCK DIAGRAM OF THE MICROPROCESSOR INTERFACE BLOCK                                        |      |

| 6     | 3.1 THE MICROPROCESSOR INTERFACE BLOCK SIGNALS                                                                   | 43   |

|       | TABLE 12: XRT75L06D MICROPROCESSOR INTERFACE SIGNALS                                                             | . 43 |

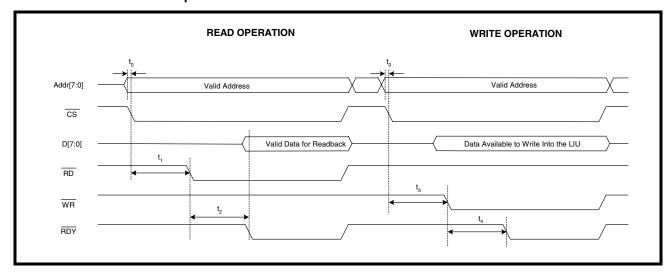

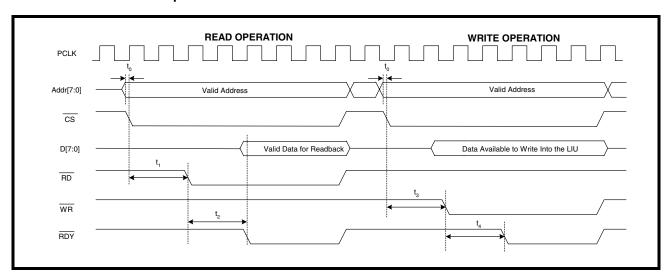

| •     | 3.2 ASYNCHRONOUS AND SYNCHRONOUS DESCRIPTION                                                                     |      |

| •     | Figure 35. Asynchronous µP Interface Signals During Programmed I/O Read and Write Operations                     |      |

|       | TIGURE 33. ASTNCHRONOUS IF INTERFACE SIGNALS DURING PROGRAMMED I/O NEAD AND WRITE OPERATIONS                     |      |

|       | FIGURE 36. SYNCHRONOUS µP INTERFACE SIGNALS DURING PROGRAMMED I/O READ AND WRITE OPERATIONS                      |      |

|       | TABLE 14: SYNCHRONOUS TIMING SPECIFICATIONS                                                                      |      |

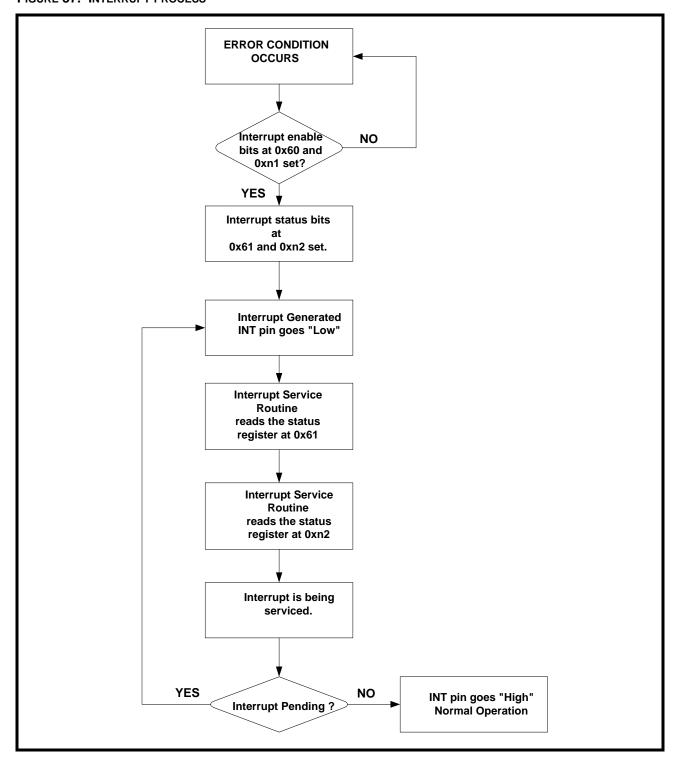

|       | FIGURE 37. INTERRUPT PROCESS.                                                                                    |      |

|       |                                                                                                                  |      |

|       | 6.2.1 HARDWARE RESET:                                                                                            |      |

|       | TABLE 15: REGISTER MAP AND BIT NAMES                                                                             | _    |

|       | TABLE 16: REGISTER MAP DESCRIPTION - GLOBAL                                                                      | _    |

|       | TABLE 17: REGISTER MAP AND BIT NAMES - CHANNEL N REGISTERS (N = 0,1,2,3,4,5)                                     |      |

|       | TABLE 18: REGISTER MAP DESCRIPTION - CHANNEL N                                                                   |      |

|       | THE SONET/SDH DE-SYNC FUNCTION WITHIN THE LIU                                                                    |      |

| 7     | 7.1 BACKGROUND AND DETAILED INFORMATION - SONET DE-SYNC APPLICATIONS                                             |      |

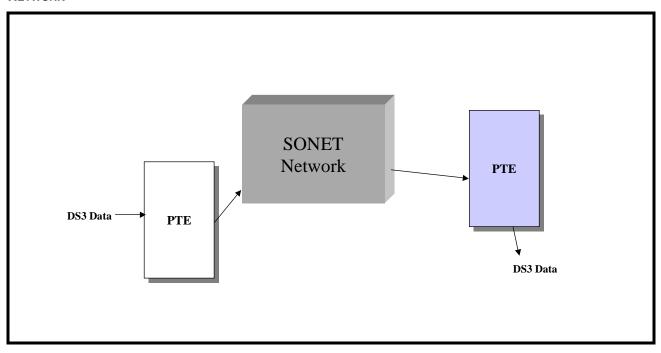

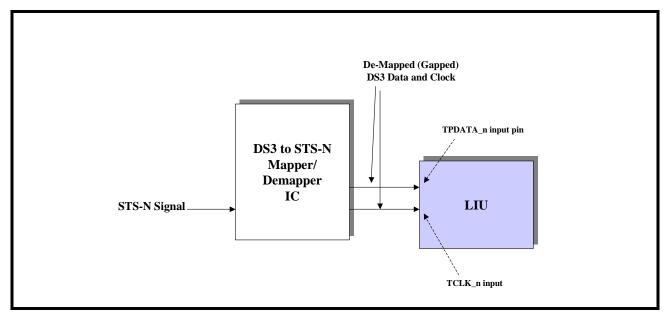

|       | FIGURE 38. A SIMPLE ILLUSTRATION OF A DS3 SIGNAL BEING MAPPED INTO AND TRANSPORTED OVER THE SONET NETWORK        | 57   |

| 7     | 7.2 MAPPING/DE-MAPPING JITTER/WANDER                                                                             | 58   |

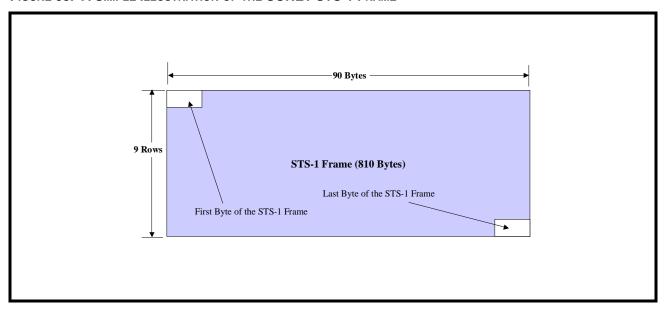

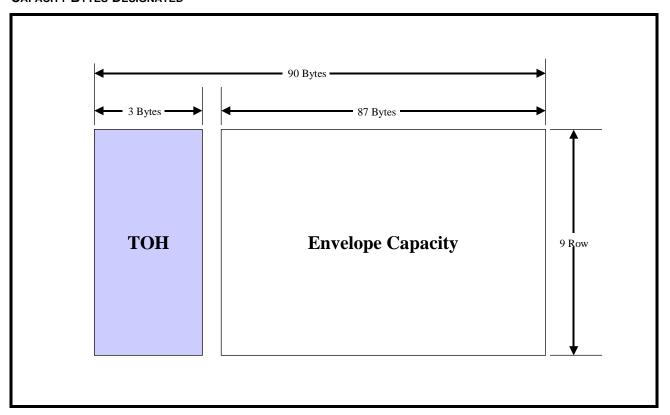

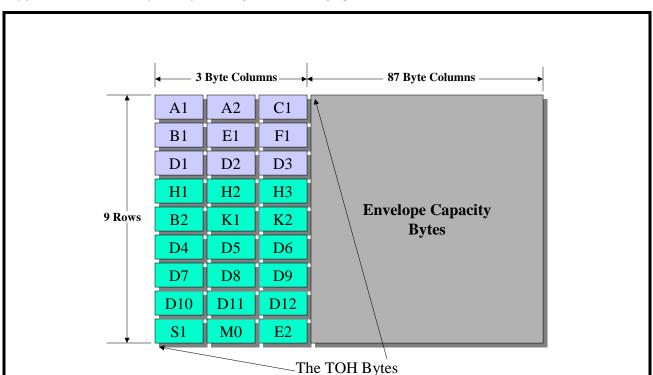

|       | 7.2.1 HOW DS3 DATA IS MAPPED INTO SONET                                                                          | 58   |

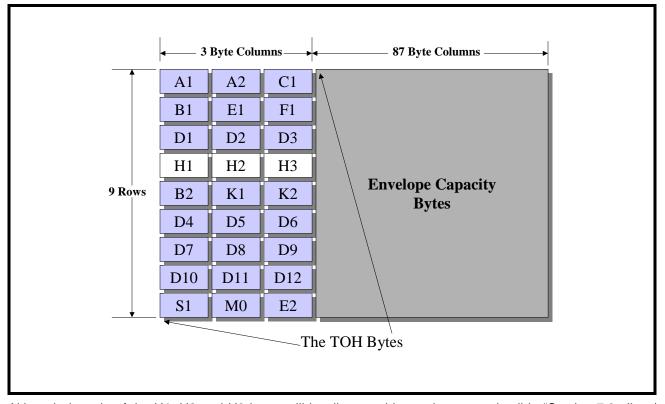

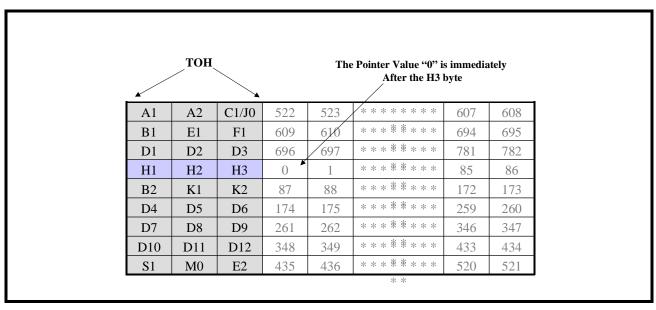

|       | FIGURE 39. A SIMPLE ILLUSTRATION OF THE SONET STS-1 FRAME                                                        |      |

|       | FIGURE 40. A SIMPLE ILLUSTRATION OF THE STS-1 FRAME STRUCTURE WITH THE TOH AND THE ENVELOPE CAPACITY BYTES DESIG |      |

REV. 1.0.4

| 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Figure 41. The Byte-Format of the TOH within an STS-1 Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                  |

| Figure 42. The Byte-Format of the TOH within an STS-1 Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                  |

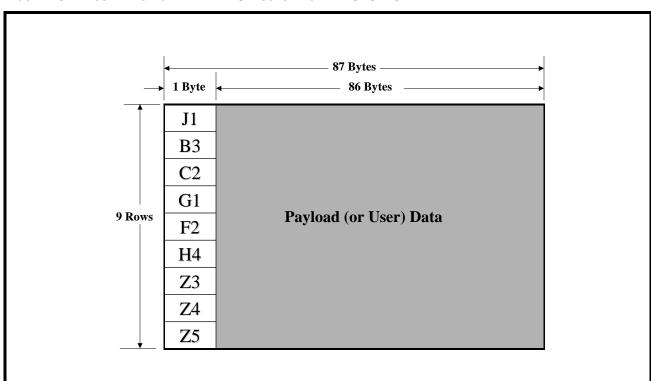

| Figure 43. Illustration of the Byte Structure of the STS-1 SPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

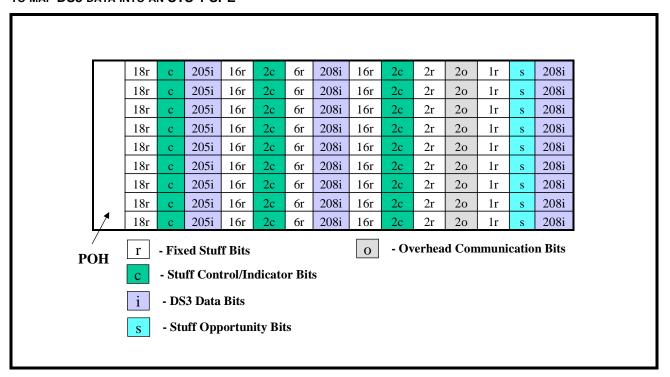

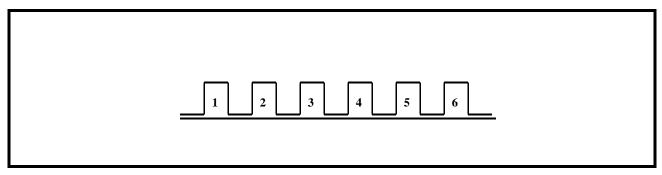

| FIGURE 44. AN ILLUSTRATION OF TELCORDIA GR-253-CORE'S RECOMMENDATION ON HOW MAP DS3 DATA INTO AN STS-1 SPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |

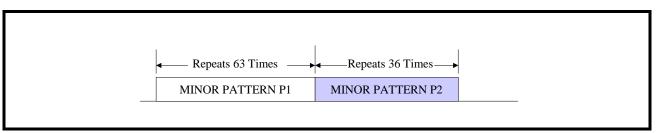

| FIGURE 45. A SIMPLIFIED "BIT-ORIENTED" VERSION OF TELCORDIA GR-253-CORE'S RECOMMENDATION ON HOW TO MAP DS3 DA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |

| AN STS-1 SPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

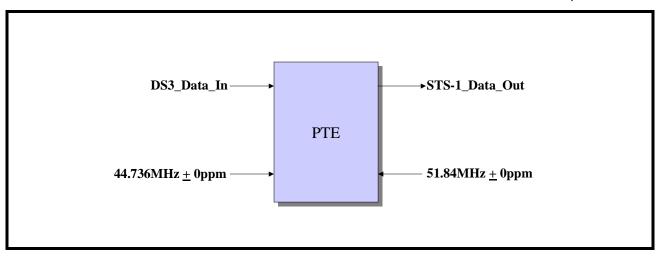

| 7.2.2 DS3 FREQUENCY OFFSETS AND THE USE OF THE "STUFF OPPORTUNITY" BITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |

| Figure 46. A Simple Illustration of a DS3 Data-Stream being Mapped into an STS-1 SPE, via a PTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |

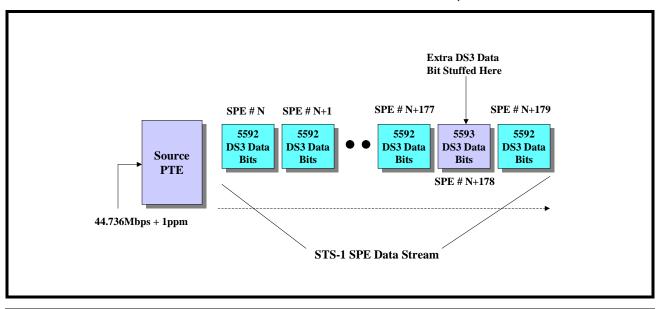

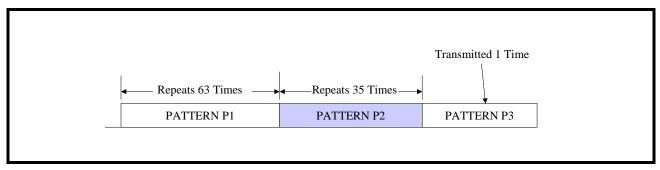

| FIGURE 47. AN ILLUSTRATION OF THE STS-1 SPE TRAFFIC THAT WILL BE GENERATED BY THE "SOURCE" PTE, WHEN MAPPING IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |

| SIGNAL THAT HAS A BIT RATE OF 44.736MBPS + 1PPM, INTO AN STS-1 SIGNAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

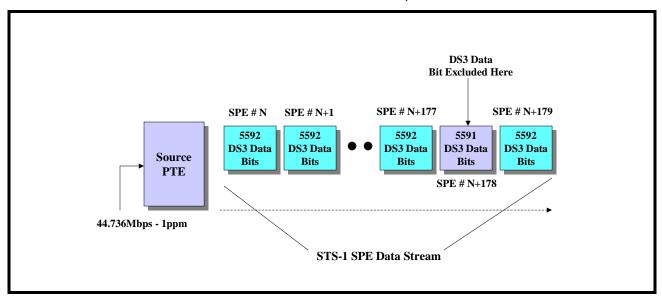

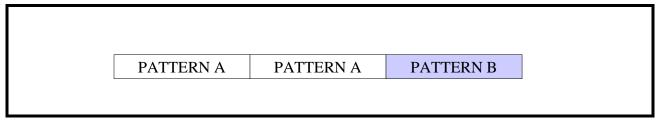

| FIGURE 48. AN ILLUSTRATION OF THE STS-1 SPE TRAFFIC THAT WILL BE GENERATED BY THE SOURCE PTE, WHEN MAPPING A DS3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                    |

| THAT HAS A BIT RATE OF 44.736MBPS - 1PPM, INTO AN STS-1 SIGNAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

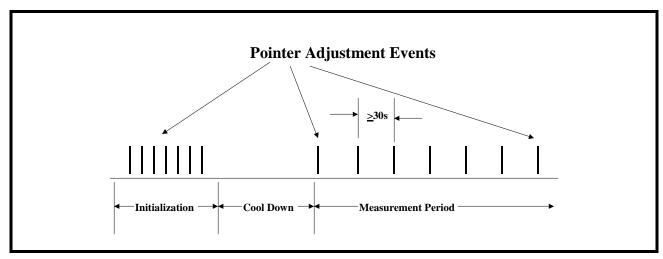

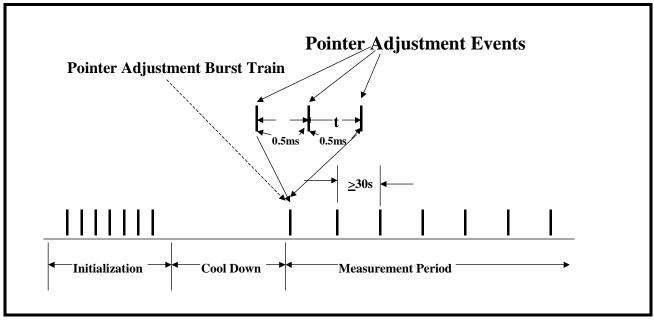

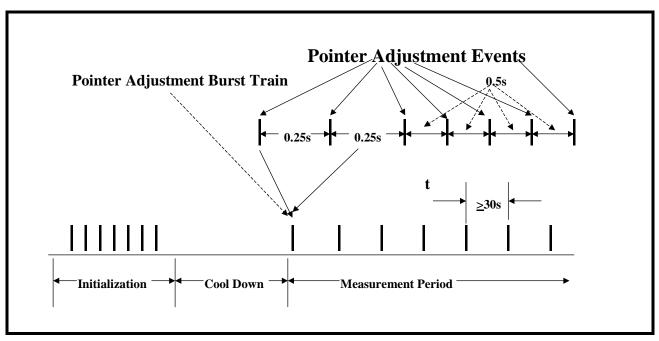

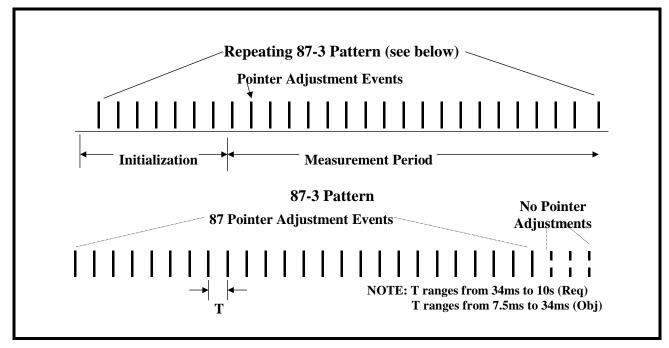

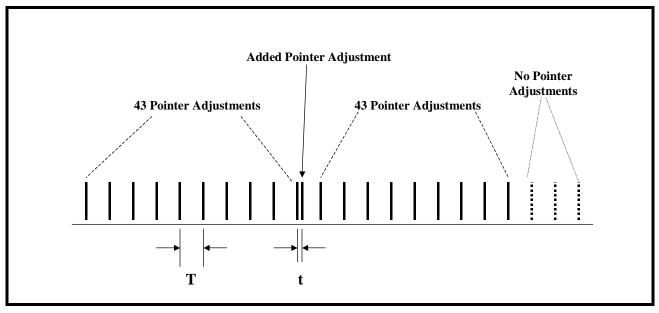

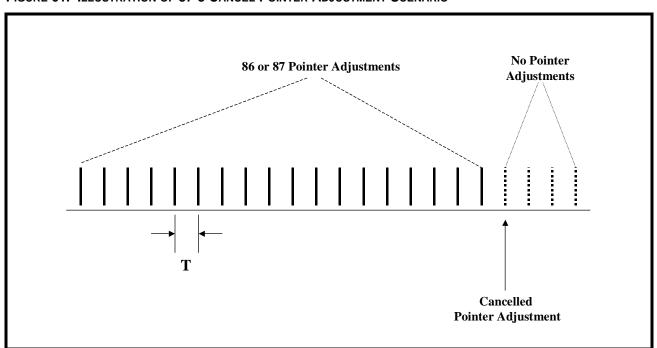

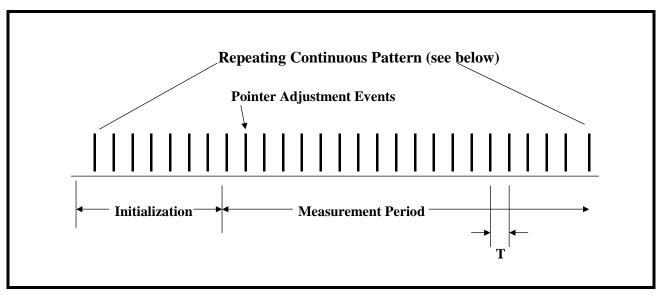

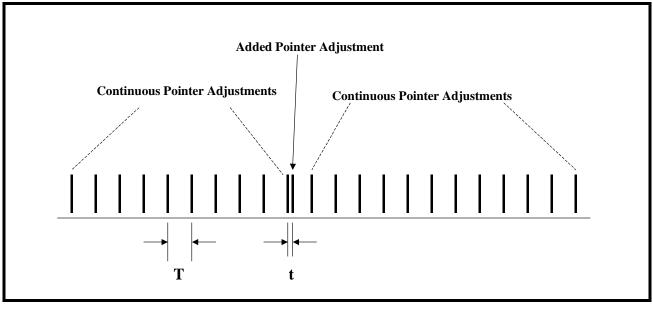

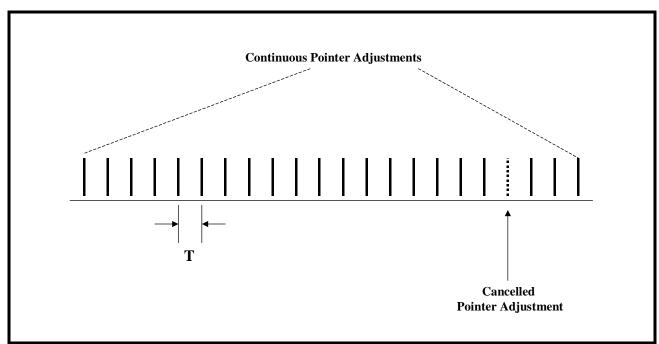

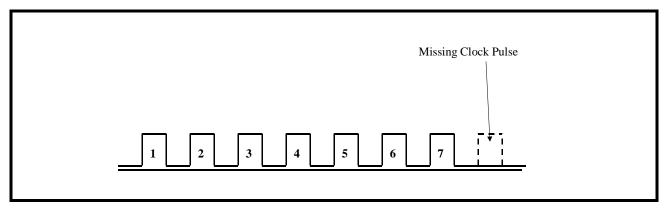

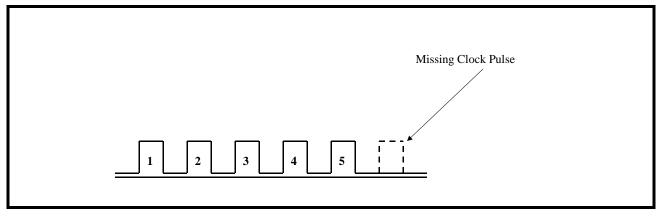

| 7.3 JITTER/WANDER DUE TO POINTER ADJUSTMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

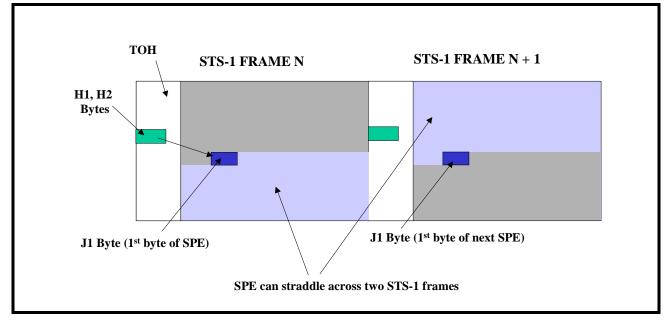

| 7.3.1 THE CONCEPT OF AN STS-1 SPE POINTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |

| FIGURE 49. AN ILLUSTRATION OF AN STS-1 SPE STRADDLING ACROSS TWO CONSECUTIVE STS-1 FRAMES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |

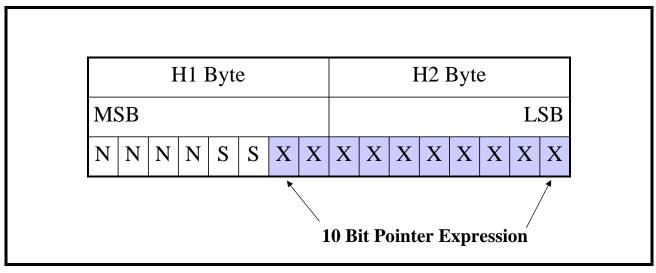

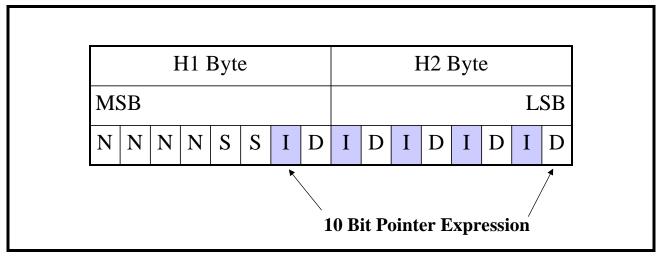

| FIGURE 50. THE BIT-FORMAT OF THE 16-BIT WORD (CONSISTING OF THE H1 AND H2 BYTES) WITH THE 10 BITS, REFLECTING THE LC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

| OF THE J1 BYTE, DESIGNATED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |

| FIGURE 51. THE RELATIONSHIP BETWEEN THE CONTENTS OF THE "POINTER BITS" (E.G., THE 10-BIT EXPRESSION WITHIN THE H1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                    |

| BYTES) AND THE LOCATION OF THE J1 BYTE WITHIN THE ENVELOPE CAPACITY OF AN STS-1 FRAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| 7.3.2 POINTER ADJUSTMENTS WITHIN THE SONET NETWORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

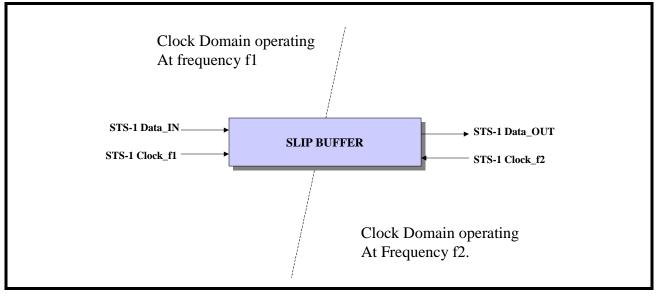

| 7.3.3 CAUSES OF POINTER ADJUSTMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

| FIGURE 52. AN ILLUSTRATION OF AN STS-1 SIGNAL BEING PROCESSED VIA A SLIP BUFFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |

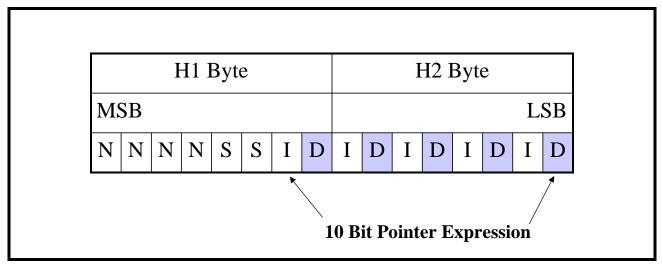

| FIGURE 53. AN ILLUSTRATION OF THE BIT FORMAT WITHIN THE 16-BIT WORD (CONSISTING OF THE H1 AND H2 BYTES) WITH THE "I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

| DESIGNATED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |

| FIGURE 54. AN ILLUSTRATION OF THE BIT-FORMAT WITHIN THE 16-BIT WORD (CONSISTING OF THE H1 AND H2 BYTES) WITH THE "I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |