Single Mode Bluetooth Low Energy (BLE) Module Part # BL600-SA, BL600-SC, BL600-ST, BL620-SA, BL620-SC, BL620-ST

Version 3.0

Hardware Integration Guide

# **REVISION HISTORY**

| Ver. | Date         | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Approver      |

|------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1.0  | 16 Apr 13    | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Jonathan Kaye |

| 1.1  | 5 July13     | Added:  To Table 1, smartBASIC runtime engine FW upgrade via UART.  To Table 1, smartBASIC application download via OTA.  Section 3.3.4 OTA (Over-the-Air) smartBASIC Application Download  Updated:                                                                                                                                                                                                                                                                                                                                                                                                          |               |

|      |              | <ul> <li>Table 1 – make it clear number of SPI (x1), I2C(x1) interfaces and ADC channels.</li> <li>Table 2 – (pin list), footnote mentions SIO_7 has Internal Pull down (default in FW).</li> <li>5.2.1 Clocks section – corrected 32.768 crystal accuracy to +/-20ppm. Added 16MHz crystal accuracy (+/-10ppm).</li> <li>6.1 Circuit section – circuit HW integration suggestion), on SIO_7 pin and Over the Air smartBASIC application download feature.</li> <li>Figure 14: BL600 Mechanical drawings – BL600 Mechanical drawing to add measurements of the half-moon shaped positioning holes.</li> </ul> | Jonathan Kaye |

| 1.2  | 25 Oct 2013  | Updated Recommended Operating Parameters notes to reflect 2.7 $\mbox{\it ms}$ rather than 2.7 $\mbox{\it \mu s}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Jonathan Kaye |

| 1.3  | 12 Dec 2013  | Added baking schedule information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Jonathan Kaye |

| 1.4  | 20 Dec 2013  | Added: ADC (AIN) input impedance into Table 6. AIN (ADC) impedance and external voltage divider setup into the 6.1 Circuit.section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Jonathan Kaye |

| 1.5  | 10 Jan 2014  | Updated TOC with correct page numbers.  Added noted regarding smartBASIC firmware's lack of support for GPIO high drive state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Jonathan Kaye |

| 1.6  | 06 Feb 2014  | Updated Bluetooth SIG Qualification section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Jonathan Kaye |

| 1.7  | 18 Feb 2014  | Updated Operating temperature range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Jonathan Kaye |

| 1.8  | 04 April2014 | <ul> <li>Updated or added the following for the BL600-Sx-04:</li> <li>Lower power consumption figures (standby doze, deep sleep) and lower peripheral (UART, SPI, I2C, ADC) block currents for the BL600-Sx-04 (new Nordic silicon).</li> <li>Improved UART with deep RX buffer (6 bytes instead of 2 bytes).</li> <li>Increased the Absolute Max rating on the VCC pin from 3.6V to 3.9V.</li> <li>Added a note for External 12K resistor to GND on SWDCLK pin NOT required on BL600-Sx-04.</li> </ul>                                                                                                       | Jonathan Kaye |

|      |              | <ul> <li>Added the following for all BL600 module revisions to align with FW features:</li> <li>Section on PWM output and FREQ output signals.</li> <li>Note on GPIO high drive strength (5 mA).</li> <li>Note regarding internal DCDC convertor turned OFF on recommendation from chipset supplier until further notice.</li> </ul>                                                                                                                                                                                                                                                                          |               |

Hardware Integration Guide

| Ver. | Date          | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Approver      |

|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|      |               | <ul> <li>Updated Peak current consumption figures with DCDC turned OFF (with internal LDO ON).</li> <li>Added in the pin list the newly FW (1.5.66.0, April 2014) enabled internal pull-ups to prevent inputs from floating and to help with the issue of Standby Doze current drifting with time.</li> <li>Note on added coming out from Deep Sleep to Standby Doze through GPIO signal through the reset vector.</li> <li>New function to detect GPIO change with no current consumption, so UART closed but still able to detect for incoming data and be woken up so that the UART can be reopened at the expense of losing that first character.</li> <li>Note that SIO_7 and AutoRUN (SIO_28) are not both high (externally), otherwise cannot load smartBASIC application script.</li> <li>Note on each module GND pin that must be connected to host PCB GND.</li> </ul> |               |

| 1.9  | 11 June 2014  | Updated BT SIG information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Jonathan Kaye |

| 2.0  | 2 July 2014   | Important information on pin 22 (reset) and pin 23 (SWDCLK).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Jonathan Kaye |

| 2.1  | 14 July 2014  | Updated SIO VIL max value in table 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Jonathan Kaye |

| 2.2  | 17 Oct 2014   | Added BL620 module information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Jonathan Kaye |

|      | 24 Oct 2014   | Added QD ID and note to section 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |

| 2.3  | 30 April 2015 | Updated Antenna information in 6.5 External Antenna Integration with BL600-SC and BL600-ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Jonathan Kaye |

| 2.4  | 01 June 2015  | Updated the BT SIG Qualification section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Jonathan Kaye |

| 2.5  | 10 Sept 2015  | Added BL600-SA-32 part number to Ordering Info section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Jonathan Kaye |

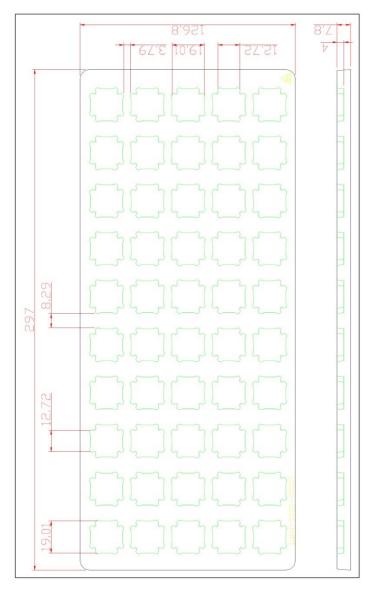

| 3.0  | 19 April 2015 | New template. Updated Land Pattern.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Jonathan Kaye |

## Hardware Integration Guide

# **C**ONTENTS

| 1 | Ove  | rview and Key Features                                            | 5    |

|---|------|-------------------------------------------------------------------|------|

| 2 | Spec | cifications                                                       | 6    |

| 3 | Hard | dware Specifications                                              | 9    |

|   | 3.1  | Block Diagram and Pin-out                                         | 9    |

|   | 3.2  | Pin Definitions                                                   | . 10 |

|   | 3.3  | Electrical Specifications                                         | . 13 |

|   | 3.3. | 1 Absolute Maximum Ratings                                        | . 13 |

|   | 3.3. | 2 Recommended Operating Parameters                                | . 13 |

|   | 3.3. | nAutoRUN Pin and Operating Modes                                  | . 15 |

|   | 3.3. | OTA (Over-the-Air) <i>smart</i> BASIC Application Download        | . 15 |

| 4 | Pow  | er Consumption                                                    | . 16 |

|   | 4.2  | Measured Peak Current Waveforms during Advertising and Connection | . 18 |

|   | 4.3  | Peripheral Block Current Consumption                              | . 20 |

| 5 | Fund | tional Description                                                | . 21 |

|   | 5.1  | Power Management (includes brown-out and power on reset)          | . 21 |

|   | 5.2  | Clocks and Timers                                                 | . 22 |

|   | 5.2. | 1 Clocks                                                          | . 22 |

|   | 5.2. | 2 Timers                                                          | . 22 |

|   | 5.3  | Memory for smartBASIC Application Code                            | . 22 |

|   | 5.4  | RF                                                                | . 23 |

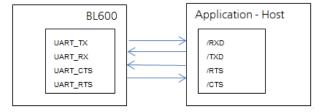

|   | 5.5  | UART Interface                                                    | . 23 |

|   | 5.6  | SPI Bus                                                           | . 24 |

|   | 5.7  | I2C Interface                                                     | . 24 |

|   | 5.8  | General Purpose I/O, ADC, PWM/FREQ and Quadrature Decoder         | . 25 |

|   | 5.8. | 1 GPIO                                                            | . 25 |

|   | 5.8. | 2 Quadrature Decoder                                              | . 25 |

Hardware Integration Guide

## 1. Overview and Key Features

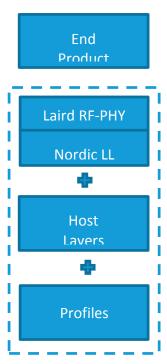

This Hardware Integration Guide also applies to the Laird BL620. The BL620 uses the same module hardware as the BL600 but it has a new firmware that supports Central mode connectivity.

Note that the BL620 module supports a JTAG upgrade but has no capability to upgrade via UART.

Every BL600 Series module is designed to enable OEMs to add single-mode Bluetooth Low Energy (BLE) to small, portable, power-conscious devices. The BL600 modules are enabled with Laird's *smart* BASIC, an event-driven programming language that enables OEMs to make their BLE product development quicker and simpler, significantly reducing time to market. *smart* BASIC enables customers to develop a complete embedded application inside the compact BL600 hardware, connecting to a wide array of external sensors via its I2C, SPI, UART, ADC or GPIO interfaces.

Based on the world-leading Nordic Semiconductor nRF51822 chipset, the BL600 modules provide ultra-low power consumption with outstanding wireless range via 4 dBm of transmit power. A broad range of BLE profiles including Temperature and Heart Rate are available and *smart* BASIC provides the ideal mechanism to support any BLE profile development of your choice. This document should be read in conjunction with the *smart* BASIC user manual.

### **Features and Benefits**

- Bluetooth v4.0 Single Mode

- External or Internal Antennas

- smartBASIC programming language

- Full Bluetooth EPL

- Compact Footprint

- Programmable TX power 4 dBm to -20 dBm

- TX whisper mode (-30 dBm, -55 dBm)

- RX sensitivity: -91 dBm

- Ultra-low power consumption

- TX: 11.6 mA peak (at +4 dBm) (refer to Note1 in Power Consumption section)

- RX: 8.8 mA peak (refer to Note1 in Power Consumption section)

- Standby Doze: 2.6 uA typical

- Deep Sleep: 0.6 uA (refer to Note4 in Power Consumption section)

- UART, GPIO, ADC, PWM, FREQ output, TIMERS, I2C, and SPI interfaces

- Fast Time to Market

- FCC, CE, IC, Taiwan (-SA version only) and Japan certified; other regulatory certifications on request

- No external components required

## **Application Areas**

- Medical devices

- Wellness devices

- iOS "appcessories"

- Fitness sensors

- Location Awareness

- Home automation

Hardware Integration Guide

# 2. SPECIFICATIONS

# 2.1 Specification Summary

| able 1: Specifications  Categories | Feature                        | Implementation                                                                |  |  |  |

|------------------------------------|--------------------------------|-------------------------------------------------------------------------------|--|--|--|

| Wireless Specification             | Bluetooth®                     | V4.0 – Single Mode                                                            |  |  |  |

|                                    |                                | Slave (from base FW v1.1.50.0 onwards)                                        |  |  |  |

|                                    | Frequency                      | 2.402 - 2.480 GHz                                                             |  |  |  |

|                                    | Maximum Transmit Power Setting | 4 dBm Conducted BL600-SA                                                      |  |  |  |

|                                    |                                | 4 dBm Conducted BL600-SC                                                      |  |  |  |

|                                    |                                | ~2.5 dBm Conducted BL600-ST (RSMA connector                                   |  |  |  |

|                                    |                                | on dev board)                                                                 |  |  |  |

|                                    | Minimum Transmit Power Setting | -20 dBm (in 4 dB steps) with smartBASIC command                               |  |  |  |

|                                    |                                | -16 dBm                                                                       |  |  |  |

|                                    |                                | -12 dBm                                                                       |  |  |  |

|                                    |                                | - 8 dBm                                                                       |  |  |  |

|                                    |                                | - 4 dBm                                                                       |  |  |  |

|                                    |                                | 0 dBm                                                                         |  |  |  |

|                                    | TX Whisper Mode 1 Transmit     | -30 dBm (min) with <i>smart</i> BASIC command                                 |  |  |  |

|                                    | Power                          |                                                                               |  |  |  |

|                                    | TX Whisper Mode 2 Transmit     | -55 dBm (min) with <i>smart</i> BASIC command                                 |  |  |  |

|                                    | Power                          |                                                                               |  |  |  |

|                                    | Receive Sensitivity            | -91 dBm typical                                                               |  |  |  |

|                                    | (0.1% BER)                     |                                                                               |  |  |  |

|                                    | Link Budget                    | 95 dB (@ 1 Mbps)                                                              |  |  |  |

|                                    | Range                          | Up to 100 m in free space                                                     |  |  |  |

|                                    | TX Whisper Modes               | Range reduction feature with TX Whisper modes with <i>smartBASIC</i> command. |  |  |  |

|                                    | Range                          | <~30 cm                                                                       |  |  |  |

|                                    | (TX Whisper Mode 2)            |                                                                               |  |  |  |

|                                    | Raw Data Rates                 | 1 Mbps (over the air)                                                         |  |  |  |

| Host Interface and                 | TOTAL                          | 28 x Multifunction I/O lines                                                  |  |  |  |

| Peripherals                        | UART                           | TX, RX, CTS, RTS                                                              |  |  |  |

| •                                  |                                | DCD, RI, DTR, DSR, CTS, RTS (Note 1)                                          |  |  |  |

|                                    |                                | Default 9600, n,8, 1                                                          |  |  |  |

|                                    |                                | From 1,200 to 115,200bps                                                      |  |  |  |

|                                    |                                | BL600-Sx-04 onwards has improved UART with Deep RX                            |  |  |  |

|                                    |                                | buffer (6 bytes instead 2 bytes).                                             |  |  |  |

|                                    | GPIO                           |                                                                               |  |  |  |

|                                    | GI 10                          | Up to 28, with configurable: I/O direction,                                   |  |  |  |

|                                    |                                | O/P drive strength (standard 0.5 mA or high 5 mA),                            |  |  |  |

|                                    | 100                            | Pull-up /pull-down                                                            |  |  |  |

|                                    | ADC                            | Six 10-bit channels (including ADC reference) 10 bit resolution               |  |  |  |

|                                    |                                | 1.2 V internal reference                                                      |  |  |  |

|                                    |                                |                                                                               |  |  |  |

|                                    | PWM or FREQ output             | 1/1, 2/3, 1/3 pre-scaling                                                     |  |  |  |

|                                    | r wivi of FREQ output          | Output a PWM or FREQ output on up to two GPIO output pins.                    |  |  |  |

|                                    |                                |                                                                               |  |  |  |

|                                    |                                | PWM output duty cycle 0%-100%                                                 |  |  |  |

Hardware Integration Guide

| Categories        | Feature                                                        | Implementation                                                                                                                                                                                                                                                                                                                 |                                                   |  |

|-------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|

|                   |                                                                | FREQ output frequency                                                                                                                                                                                                                                                                                                          | 0 MHz-4 MHz<br>(50% duty cycle)                   |  |

|                   | 12C                                                            | One I2C interface (up to 4                                                                                                                                                                                                                                                                                                     | 00 kbps) (Note 2)                                 |  |

|                   | SPI                                                            | One SPI Master interface (                                                                                                                                                                                                                                                                                                     | (up to 4 Mbps) (Note 3)                           |  |

| Profiles          | Services supported<br>(Note 4)<br>(FW v1.1.50.0)               | <ul> <li>Heart Rate Service</li> <li>Health Thermometer</li> <li>Battery Alert Service</li> <li>Blood Pressure Service</li> <li>Device Information S</li> <li>Immediate Alert Service</li> <li>IOPT (Interoperabilit</li> <li>Link Loss Service</li> <li>Transmit Power Service</li> <li>Custom services (from base</li> </ul> | ce<br>Gervice<br>vice<br>y)                       |  |

| FW Upgrade        | smart BASIC runtime engine FW upgrade (Note 5)                 | Via JTAG. Using the supplication Via UART.  Note: The BL620 supports capability to upgrade via U                                                                                                                                                                                                                               | s a JTAG upgrade but has no                       |  |

| Programmability   | smart BASIC                                                    | On-board programming language similar to BASIC.                                                                                                                                                                                                                                                                                |                                                   |  |

|                   | smart BASIC application<br>download                            | (1) Via UART.<br>(2) Via Over the Air (if SIO externally).                                                                                                                                                                                                                                                                     | _7 pin is pulled high                             |  |

| Control Protocols | Any                                                            | User defined via smartBAS                                                                                                                                                                                                                                                                                                      | SIC                                               |  |

| Operating Modes   | Self-contained Run mode                                        | Selected by nAutoRun pin LOW (0V). Then runs \$autoscript) if it exists.                                                                                                                                                                                                                                                       | status:<br>orun\$ ( <i>smart</i> BASIC applicatio |  |

|                   | Interactive / development mode                                 | HIGH (VCC). Then runs via at+run (and "file name" of smartBASIC application script).                                                                                                                                                                                                                                           |                                                   |  |

| Supply Voltage    | Supply (VCC)                                                   | 2.1 – 3.6 V – internal DCDO<br>1.8 – 3.6 V – internal LDO<br>DCDC switched on if VCC>                                                                                                                                                                                                                                          |                                                   |  |

| Power Consumption | Active Modes Peak Current (for<br>Max TX PWR 4 dBm)            | Advertising or Connected mode                                                                                                                                                                                                                                                                                                  | 11.6 mA peak TX<br>8.9 mA peak RX                 |  |

|                   | Active Modes Peak Current for TX<br>Whisper mode2 PWR -55 dBm) | Advertising or Connected mode                                                                                                                                                                                                                                                                                                  | 5 mA peak TX<br>8.5 mA peak RX                    |  |

|                   | Active Modes Average Current                                   | Depends on many factors,                                                                                                                                                                                                                                                                                                       | see Power Consumption.                            |  |

|                   | Ultra-Low Power Modes                                          | Standby Doze                                                                                                                                                                                                                                                                                                                   | 2.6 uA typical (Note 6)                           |  |

|                   |                                                                | Deep Sleep                                                                                                                                                                                                                                                                                                                     | 600 nA (Note 6)                                   |  |

| Antenna Options   | Internal                                                       |                                                                                                                                                                                                                                                                                                                                | ntenna – on-board BL600-SA                        |  |

|                   | External – Option 1                                            | Dipole antenna (with IPEX Dipole PCB antenna (with                                                                                                                                                                                                                                                                             |                                                   |  |

|                   |                                                                | Connection via IPEX MH4                                                                                                                                                                                                                                                                                                        |                                                   |  |

Hardware Integration Guide

| Categories               | Feature             | Implementation                       |

|--------------------------|---------------------|--------------------------------------|

|                          |                     | Connection via Trace Pads – BL600-ST |

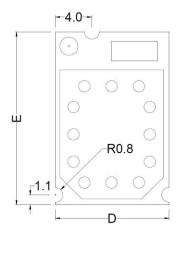

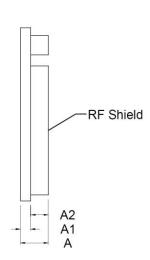

| Physical                 | Dimensions          | 19 mm x 12.5 mm x 3 mm               |

|                          | Weight              | <1 gram                              |

| Environmental            | Operating           | -25 °C to +75 °C (VCC 1.8V-3.6V)     |

|                          |                     | -40 °C to +85 °C (VCC 3.3V+/-10%)    |

|                          | Storage             | -40 °C to +85 °C                     |

| Miscellaneous            | Lead Free           | Lead-free and RoHS compliant         |

|                          | Warranty            | 5-Year Limited Lifetime              |

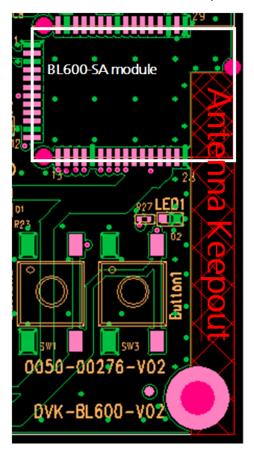

| <b>Development Tools</b> | Development Kit     | Development Kit DVK-BL600-Sx and     |

|                          |                     | Free Software Tools                  |

| Approvals                | Bluetooth®          | End Product Listing (EPL)            |

|                          | FCC / IC / CE / MIC | All BL600 Series                     |

- **Note 1:** DSR, DTR, RI, and DCD can be implemented in the *smart* BASIC application.

- **Note 2:** With I2C interface selected, pull-up resistors on I2C SDA and I2C SCL MUST be connected externally as per I2C standard.

- **Note 3:** SPI interface (master) consists of SPI MOSI, SPI MISO and SPI CLK. SPI CS is created by customer using any spare SIO pin within their *smart*BASIC application script allowing multi-dropping.

- **Note 4:** BL600 module comes loaded with *smart* BASIC runtime engine FW, but does not come loaded with any *smart* BASIC application script (as that is dependent on customer end application or use). Laird provides many sample *smart* BASIC application scripts covering the services listed. Additional BLE services being added every quarter.

- **Note 5:** *smart* BASIC runtime engine firmware v1.2.54.0 (Jun2013) and subsequent versions, the internal DCDC convertor was switched off on recommendation from the chipset provider until future notice.

- Note 6: Measured with BL600-Sx-04.

Deep Sleep current for BL600-Sx-02 and BL600-Sx-03 ~1000nA (typical).

Standby Doze current for BL600-Sx-02 and BL600-Sx-03 Standby Doze current 3.5uA (typical).

- **Note 7:** PWM output signal has a frequency and duty cycle property. PWM output is generated using 32-bit hardware timers. The timers are clocked by a 1MHz (1uS period) clock source. Trade-off PWM output frequency with resolution. For example:

PWM output frequency of 500kHz (2uS) results in resolution of 1:2

PWM output frequency of 100kHz (10uS) results in resolution of 1:10

PWM output frequency of 10kHz (100uS) results in resolution of 1:100

PWM output frequency of 1kHz(1000uS) results in resolution of 1:1000

Refer to the *smartBASIC* user guide for details.

© Copyright 2015 Laird. All Rights Reserved

Americas: +1-800-492-2320

## 3. HARDWARE SPECIFICATIONS

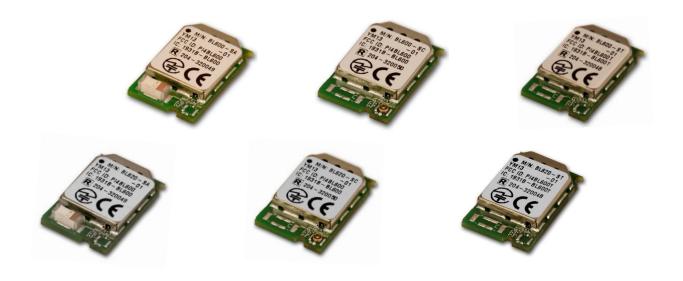

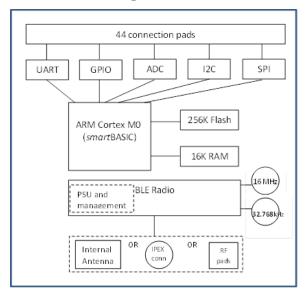

## 3.1 Block Diagram and Pin-out

Figure 1: Functional HW and SW block Diagram for BL600 series BLE smartBASIC module

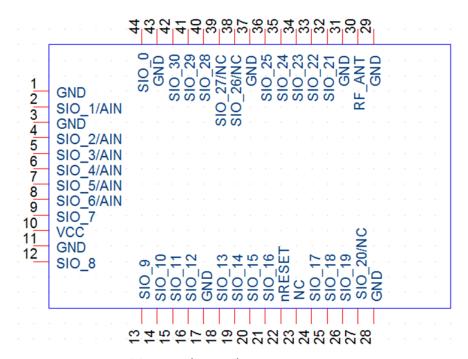

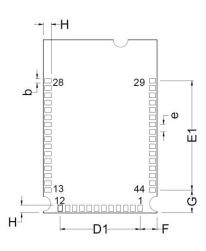

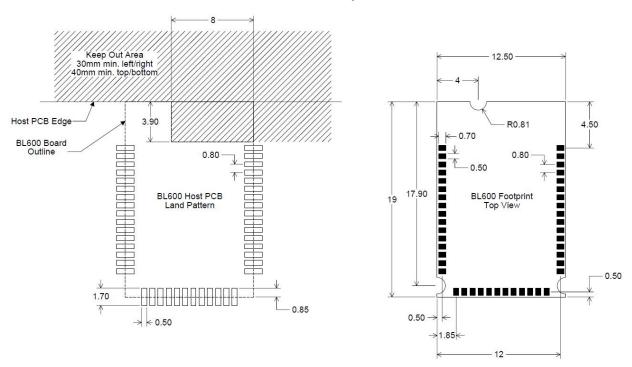

Figure 2: BL600-Sx module pin-out (top view).

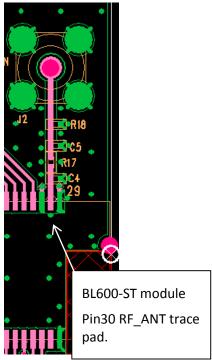

Note: Pin 30 (RF\_ANT) is for BL600-ST only. On the BL600-SA and BL600-SC, pin 30 is NC.

Hardware Integration Guide

## 3.2 Pin Definitions

Table 2: Pin definitions

| Table 2: | Pin definitio | ons                 |                |                                |                                  |             |                                                       |

|----------|---------------|---------------------|----------------|--------------------------------|----------------------------------|-------------|-------------------------------------------------------|

| Pin #    | Pin<br>Name   | Default<br>Function | Alt.<br>Funct. | Default<br>Direction<br>Note14 | Pull-up /<br>Pull-down<br>Note14 | Notes       | Comment                                               |

| 1        | GND           | -                   | -              | -                              | -                                | -           | -                                                     |

| 2        | SIO_1         | DIO                 | AIN            | IN                             | PULL-UP                          | 1,2,3,4,5   | 8,9,10 bit resolution. Voltage scaling 1/1, 2/3, 1/3. |

| 3        | GND           | -                   | -              | -                              | -                                | -           | -                                                     |

| 4        | SIO_2         | DIO                 | AIN            | IN                             | PULL-UP                          | 1,2,3,4,5   | 8,9,10 bit resolution. Voltage scaling 1/1, 2/3, 1/3. |

| 5        | SIO_3         | DIO                 | AIN            | IN                             | PULL-UP                          | 1,2,3,4,5   | 8,9,10 bit resolution, Voltage scaling 1/1, 2/3, 1/3. |

| 6        | SIO_4         | DIO                 | AIN            | IN                             | PULL-UP                          | 1,2,3,4,5   | 8,9,10 bit resolution, Voltage scaling 1/1, 2/3, 1/3. |

| 7        | SIO_5         | DIO                 | AIN            | IN                             | PULL-UP                          | 1,2,3,4,5   | 8,9,10 bit resolution, Voltage scaling 1/1, 2/3, 1/3. |

| 8        | SIO_6         | DIO                 | AIN            | IN                             | PULL-UP                          | 1,2,3,4,5   | 8,9,10 bit resolution, Voltage scaling 1/1, 2/3, 1/3  |

| 9        | SIO_7         | DIO                 |                | IN                             | PULL-DOWN                        | 1,2, 12, 13 | Internal Pull down (default)                          |

| 10       | VCC           | -                   | -              | -                              | -                                | -           | -                                                     |

| 11       | GND           |                     |                |                                |                                  |             |                                                       |

| 12       | SIO_8         | DIO                 | I2C SDA        | IN                             | PULL-UP                          | 1,2,4,5,6   | I2COPEN() in smartBASIC selects                       |

| 13       | SIO_9         | DIO                 | I2C SCL        | IN                             | PULL-UP                          | 1,2,4,5,6   | I2C function                                          |

| 14       | SIO_10        | DIO                 | SPI MOSI       | IN                             | PULL-UP                          | 1,2,4,5,6   | SPIOPEN() in smartBASIC selects                       |

| 15       | SIO_11        | DIO                 | SPI MISO       | IN                             | PULL-UP                          | 1,2,4,5,6   | SPI function, MOSI and CLK will                       |

| 16       | SIO_12        | DIO                 | SPI CLK        | IN                             | PULL-UP                          | 1,2,4,5,6   | be outputs when in SPI master mode. See Note 11.      |

| 17       | GND           | -                   | -              | -                              | -                                | -           | <del>-</del>                                          |

| 18       | SIO_13        | DIO                 |                | IN                             | PULL-UP                          | 1,2         |                                                       |

| 19       | SIO_14        | DIO                 |                | IN                             | PULL-UP                          | 1,2         |                                                       |

| 20       | SIO_15        | DIO                 |                | IN                             | PULL-UP                          | 1,2         | Laird Devkit : Buzzer output                          |

| 21       | SIO_16        | DIO                 |                | IN                             | PULL-UP                          | 1,2         | Laird Devkit : Button 0 input                         |

| 22       | nRESET        |                     |                | IN                             |                                  | 9,10        | System Reset (Active low)                             |

| 23       | NC            |                     |                |                                |                                  | 9           | DO NOT CONNECT                                        |

| 24       | SIO_17        | DIO                 |                | IN                             | PULL-UP                          | 1,2         | Laird Devkit : Button 1 input                         |

| 25       | SIO_18        | DIO                 |                | IN                             | PULL-UP                          | 1,2         | Laird Devkit : LED 0                                  |

| 26       | SIO_19        | DIO                 |                | IN                             | PULL-UP                          | 1,2         | Laird Devkit : LED 1                                  |

| 27       | SIO_20        | NC                  |                |                                |                                  |             | Reserved for future use                               |

| 28       | GND           |                     |                |                                |                                  |             |                                                       |

| 29       | GND           |                     |                |                                |                                  |             |                                                       |

| 30       | RF_ANT        |                     |                |                                |                                  | 8           | Used on BL600-ST only.                                |

| 31       | GND           |                     |                |                                |                                  |             |                                                       |

| 32       | SIO_21        | DIO                 | UART TX        | OUT                            | Set high in<br>FW                | 1,2,4,6,7   |                                                       |

Americas: +1-800-492-2320

Hardware Integration Guide

| s DIO<br>ARTOPEN() |

|--------------------|

| behaviour          |

| _DTR via           |

|                    |

| use. Do NOT        |

|                    |

| DSR via            |

| _DCD via           |

| _RI via            |

|                    |

|                    |

| us<br>_D           |

**Note 1:** Secondary function is selectable in *smartBASIC* application.

Note 2: DIO = Digital Input or Output. I/O voltage level tracks VCC.

Note 3: AIN = Analog Input

Note 4: DIO or AIN functionality is selected using the GpioSetFunc() function in smartBASIC.

Note 5: AIN configuration selected using GpioSetFunc() function.

Note 6: I2C, UART, SPI controlled by xxxOPEN() functions in smart BASIC.

Note 7: SIO 21 to SIO 24 are DIO by default when \$autorun\$ app runs on power up.

**Note 8:** RF\_ANT pin (pin30) is on theBL600-ST module only. Customer MUST use 50-Ohm trace from RF\_ANT pin to RSMA RF connector on host PCB. More details on 50-Ohm trace design refer to section **50-OhmsRF Trace on Host PCB for BL600-ST**.

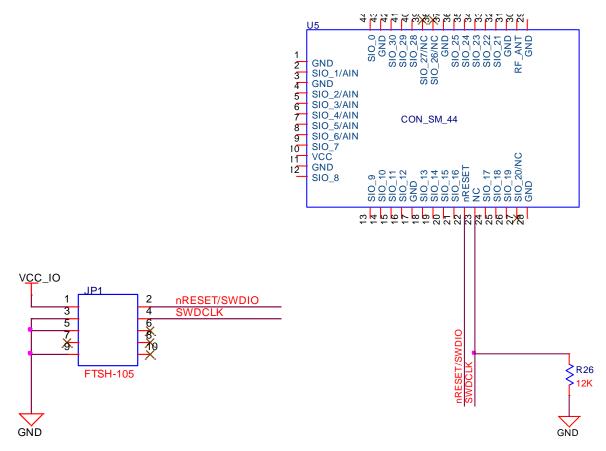

Note 9: Hidden JTAG (2-wire interface), pin22 (SWDIO) and pin23 (SWDCLK). Used for upgrading *smart*BASIC runtime engine FW only with Laird supplied J-link programmer. Using this hidden JTAG requires 12K resistor to GND (on pin23 SWDCLK) for BL600-Sx-02 and BL600-Sx-03 on customers host PCB and header connector Samtech FTSH-105-01-L-DV, refer to section *Miscellaneous (hidden JTAG)* for details. 12K resistor is NOT required on customers host PCB when using the BL600-Sx-04.

Note 10: Pull the nRESET pin (pin 22) low for minimum 100 mS in order for the BL600 to reset.

For BL600-Sx-02 or BL600-Sx-03: To ensure nReset functions properly, you MUST place a 12K resistor to GND on BL600 pin 23 (NC/SWDCLK) on your host board.

For BL600-Sx-04: Do not fit a resistor to GND on BL600 pin 23 (NC/SWDCLK).

© Copyright 2015 Laird. All Rights Reserved

Hardware Integration Guide

- **Note11:** SPI CS is created by customer using any spare SIO pin within their *smart*BASIC application script allowing multi-dropping.

- **Note12:** SIO\_7 pin has to be pulled high externally to enable OTA (over the Air) *smartBASIC* application download. Refer to the latest FW release documentation for details.

- **Note13:** User must ensure that SIO\_7 and AutoRUN(SIO\_28) are NOT BOTH HIGH (externally), otherwise in that state the UART is bridged to Virtual Serial Port service and so the BL600 module will not respond to AT commands and therefore cannot load *smart*BASIC application scripts (applies to all versions of the *smart* BASIC runtime engine firmware.

- Note14: smart BASIC runtime engine FW 1.5.66.0(Apr2014) has DIO (Default Function) INPUT pins, have by default PULL-UP enabled. This was done to avoid floating inputs (which can also cause current consumption in low power modes (e.g. StandbyDoze) to drift with time. In any case customer can disable the PUL-UP through their smart BASIC application.

ALL smart BASIC runtime engine FW versions before 1.5.66.0(Apr2014), the INPUT DIO pins have NO pull-up or pull-down enabled and would require the customer to enable pull-up through smart BASIC application script.

All the SIO pins (with a default function of DIO are inputs – apart from SIO\_21 and SIO\_23, which are outputs):

- SIO\_21 (alternative function UART\_TX) is an output, set High (in FW).

- SIO\_23 (alternative function UART\_RTS) is an output, set Low (in FW).

- SIO 22 (alternative function UART RX) is an input, set with internal pull-up (in FW).

- SIO\_24 (alternative function UART\_CTS) is an input, set with internal pull-down (in FW).

- **SIO\_7** is an input set with internal pull-down (in FW). It is used for over the air downloading of *smartBASIC* applications. Refer to the latest FW release documentation for details.

The BL600 module is delivered with the integrated *smart* BASIC runtime engine FW loaded (but no onboard *smart*BASIC application script). Because of this, it starts up in AT command mode by default.

At reset, all SIO lines are configured as the defaults shown above.

SIO lines can be configured through the *smart* BASIC application script to be either inputs or outputs with pullups or pull-downs. When an alternative SIO function is selected (such as I2C or SPI), the firmware does not allow the setup of internal pull-up/pull-down. Therefore, when I2C interface is selected, pull-up resistors on I2C SDA and I2C SCL **MUST** be connected externally as per I2C standard.

UART\_RX, UART\_TX, UART\_CTS are 3.3 V level logic (if VCC is 3.3 V, i.e. SIO pin I/O levels track VCC). For example, when RX and TX are idle, they sit at 3.3 V (if VCC is 3.3 V). Conversely, handshaking pins CTS and RTS at 0 V are treated as assertions.

Pin 40 (nAutoRUN) is an input, with active low logic. In the development kit (DVK-BL600-sx) it is connected so that the state is driven by the host's DTR output line. The nAutoRUN pin must be externally held high or low to select between the following two BL600 operating modes:

- Self-contained Run mode (nAutoRUN pin held at 0 V).

- Interactive / development mode (nAutoRUN pin held at VCC).

smartBASIC runtime engine firmware checks for the status of nAutoRUN during power-up or reset. If it is low and if there is a smartBASIC application script named **\$autorun\$**, then the smartBASIC runtime engine FW executes the application script automatically; hence the name Self-contained Run Mode.

## 3.3 Electrical Specifications

## 3.3.1 Absolute Maximum Ratings

Absolute maximum ratings for supply voltage and voltages on digital and analogue pins of the module are listed below; exceeding these values causes permanent damage.

**Table 3: Maximum Current Ratings**

| Parameter           | Minimum | Maximum       | Unit |

|---------------------|---------|---------------|------|

| Voltage at VCC pin  | -0.3    | +3.6 (Note 1) | V    |

| Voltage at GND pin  |         | 0             | V    |

| Voltage at SIO pin  | -0.3    | VCC+0.3       | V    |

| Storage temperature | -40     | +85           | ōС   |

Note 1: Absolute Max Rating for VCC pin (max) is 3.6V for BL600-Sx-02 and BL600-Sx-03. Absolute Max Rating for VCC pin (max) is 3.9V for BL600-Sx-04.

## 3.3.2 Recommended Operating Parameters

**Table 4: Power Supply Operating Parameters**

| Parameter                                     | Minimum | Typical | Maximum | Unit |

|-----------------------------------------------|---------|---------|---------|------|

| VCC (with internal LDO) <sup>1</sup>          | 1.8     | 3       | 3.6     | V    |

| VCC (with internal DCDC enabled) <sup>1</sup> | 2.1     | 3       | 3.6     | V    |

| VCC Maximum ripple or noise <sup>2</sup>      |         |         | 10      | mV   |

| VCC rise time (0 to 1.8V) <sup>3</sup>        |         |         | 60      | mS   |

| Operating Temperature Range                   |         |         |         |      |

| 3.3V +/- 10%                                  | -40     | -       | +85     | ōC   |

| (contact Laird with any queries) 1.8V         | -25     | -       | +75     | ōC   |

**Note 1:** Internal DCDC is used if VCC >2.1 V on power-up; otherwise internal LDO is used. 4.7 uF internal to module on VCC. *smart* BASIC runtime engine firmware v1.2.54.0(Jun2013) and subsequent versions, the internal DCDC convertor was switched off on recommendation from the chipset provider until future notice.

**Note 2:** The maximum VCC ripple or noise (at any frequency) that does not disturb the radio.

Note 3: The on-board power-on reset circuitry may not work for rise times outside the noted interval. Time reset is active from VCC reaches 1.7 V with 50 mS rise time is 29 mS typical. Time reset is active from VCC reaches 1.7 V with 1 uS rise time is 2.7 mS typical.

Table 5: Signal Levels for Interface, SIO

| Parameter                            | Minimum | Typical | Maximum | Unit |

|--------------------------------------|---------|---------|---------|------|

| VCC (with internal LDO) <sup>1</sup> | 0.7 VCC |         | VCC     | V    |

| VIH Input high voltage               | VSS     |         | 0.3     | V    |

| VIL Input low voltage                |         |         |         |      |

|                                      | VCC-0.3 |         | VCC     | V    |

|                                      | VCC-0.3 |         | VCC     | V    |

Hardware Integration Guide

| Parameter                  | Minimum | Typical | Maximum | Unit |

|----------------------------|---------|---------|---------|------|

| VOH Output high voltage    |         |         |         |      |

| (std. drive, 0.5mA)        | VSS     |         | 0.3     | V    |

| (high-drive, 5mA) (Note 1) | VSS     |         | 0.3     | V    |

| VOL Output low voltage     | 11      | 13      | 16      | kΩ   |

| (std. drive, 0.5mA)        |         |         |         |      |

| (high-drive, 5mA) (Note 1) |         |         |         |      |

| Pull up resistance         | 11      | 13      | 16      | kΩ   |

|                            |         |         |         |      |

**Note 1:** Maximum number of pins with 5mA high drive is three. smartBASIC firmware 1.5.65.0(Feb2014) and subsequent versions support high drive (as well standard drive).

Table 6: SIO pin alternative function AIN (ADC) specification

| Table 6: SIO pin alternative function AIN (ADC) spo<br>Parameter                                       | Minimum | Typical       | Maximum | Unit    |

|--------------------------------------------------------------------------------------------------------|---------|---------------|---------|---------|

| ADC Internal reference voltage                                                                         | -1.5%   | 1.2 V         | +1.5%   | %       |

| ADC pin input internal selectable scaling                                                              |         | 1/1, 1/3, 2/3 |         | Scaling |

| ADC input pin (AIN) voltage maximum without damaging ADC w.r.t VCC Prescaling                          |         |               |         |         |

| 3.6 V 1/1                                                                                              |         |               | 2.4     | V       |

| 3.6 V 2/3                                                                                              |         |               | 3.6     | V       |

| 3.6 V 1/3                                                                                              |         |               | 3.6     | V       |

| 3.3 V 1/1                                                                                              |         |               | 2.4     | V       |

| 3.3 V 2/3                                                                                              |         |               | 3.6     | V       |

| 3.3 V 1/3                                                                                              |         |               | 3.6     | V       |

| 1.8 V 1/1                                                                                              |         |               | 2.1     | V       |

| 1.8 V 2/3                                                                                              |         |               | 2.1     | V       |

| 1.8 V 1/3                                                                                              |         |               | 2.1     | V       |

| ADC input pin (AIN) voltage maximum without saturating ADC (with 1.2V internal reference) <sup>1</sup> |         |               |         |         |

| 1/1 prescaling                                                                                         |         |               | 1.2     | V       |

| 2/3 prescaling                                                                                         |         |               | 1.8     | V       |

| 1/3 prescaling                                                                                         |         |               | 3.6     | V       |

| Time required to convert single sample in                                                              |         |               |         |         |

| 10bit mode                                                                                             |         | 68            |         | uS      |

| 9bit mode <sup>2</sup>                                                                                 |         | 36            |         | uS      |

| 8 bit mode <sup>2</sup>                                                                                |         | 20            |         | uS      |

| ADC input impedance (during operation) <sup>3</sup>                                                    |         |               |         |         |

Hardware Integration Guide

- **Note 1:** Stay within internal 1.2 V reference voltage with given prescaling on AIN pin and do not violate ADC maximum input voltage (for damage) for a given VCC, e.g. If VCC is 1.8 V can only expose AIN pin to 2.1 V (VCC+0.3).

- **Note 2:** Currently, the *smart*BASIC runtime engine firmware only allows 10-bit mode.

- Note 3: ADC input impedance is estimated mean impedance of the ADC (AIN) pins. The tolerance is +/-20%. The ADC is highly sensitive to the impedance of the source. The ADC (AIN) input impedance is 200k-600k depending on your ADC gain (pre-scaling) setting. Normally, when not sampling, the ADC (AIN) impedance will have very high value and can consider it to be an open circuit. The moment ADC is sampling, ADC(AIN) impedance is 200k-600k.

## 3.3.3 nAutoRUN Pin and Operating Modes

Operating modes (refer to the *smart* BASIC manual for details):

- Self-contained mode

- Interactive/Development mode

Table 7: nAutoRUN pin

| Signal Name       | Pin # | 1/0 | Comments                                                                                                                                                                                     |

|-------------------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nAutoRUN (SIO_28) | 28    | I   | Input with active low logic.  Operating mode selected by nAutoRun pin status:  If Low (OV), runs \$autorun\$ if it exists;  If High (VCC), runs via at+run (and "file name" of application). |

Pin 40 (nAutoRUN) is an input, with active low logic. In the development board (DVK-BL600-sx) it is connected so that the state is driven by the host's DTR output line. nAutoRUN pin needs to be externally held high or low to select between the two BL600 operating modes:

- Self-contained Run mode (nAutoRUN pin held at 0V).

- Interactive/Development mode (nAutoRUN pin held at VCC)

smartBASIC runtime engine firmware checks for the status of nAutoRUN during power-up or reset. If it is low and if there is a smartBASIC application named \$autorun\$ then the smartBASIC runtime engine executes the application automatically; hence the name self-contained run mode.

## 3.3.4 OTA (Over-the-Air) smartBASIC Application Download

Refer to latest FW release documentation (FW release notes and *smart* BASIC user manual) for details. This feature was first added the *smart* BASIC runtime engine firmware (v1\_2\_54\_0-r2).

Table 8: OTA mode

| Signal Name | Pin # | I/O | Comments                                                                                                                                                   |

|-------------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIO_7       | 9     | I   | Internal pull down (default). OTA mode selected by externally pulling SIO_7 pin: High (VCC), then OTA <i>smart</i> BASIC application download is possible. |

The OTA *smart*BASIC application download feature can be useful for a customer's production because it allows the module to be soldered into an end product without preconfiguration; the application can then be downloaded over the air once the product has been pre-tested.

**Note:** It is the *smart* BASIC application that is downloaded over the air and NOT the firmware. Due to this principle reason for use in production, to facilitate multiple programming stations in a locality the transmit power is limited (to lower Tx power), refer to *smart* BASIC user manual for more details.

## 4. POWER CONSUMPTION

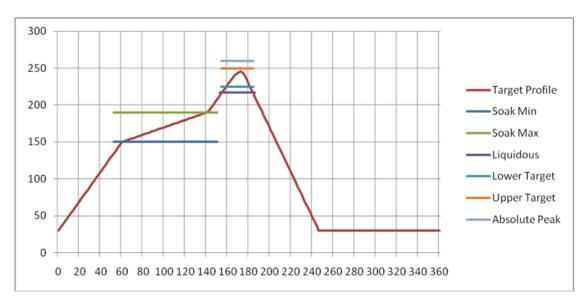

Data taken at VCC 3.3V with internal (to chipset) LDO ON or with internal (to chipset) DCDC ON (see Note1) and 25°C.

Table 9: Power consumption

| Parameter                                    | Min Typical Max     | Unit |  |  |

|----------------------------------------------|---------------------|------|--|--|

| Active Mode 'peak' current – Note 1          | With LDO (withDCDC) |      |  |  |

| (Advertising or Connection)                  |                     |      |  |  |

| TX only run peak current @TXpwr= +4 dBm      | 16 (11.6)           | mA   |  |  |

| TX only run peak current @T pwr= 0 dBm       | 10.5 (8.4)          | mA   |  |  |

| TX only run peak current @TXpwr= -4 dBm      | 8 (7.1)             | mA   |  |  |

| TX only run peak current @TXpwr= -8 dBm      | 7 (6.9)             | mA   |  |  |

| TX only run peak current @TXpwr= -12 dBm     | 6.5 (6.4)           | mA   |  |  |

| TX only run peak current @TXpwr= -16 dBm     | 6 (6.1)             | mA   |  |  |

| T X only run peak current @TXpwr= -20 dBm    | 5.5 (5.5)           | mA   |  |  |

| TX Whisper Mode 1 (Note 2)                   |                     |      |  |  |

| TX only run peak current @TXpwr= -30 dBm     | 5.5 (5.4)           | mA   |  |  |

| TX Whisper Mode 2 (Note 2)                   |                     |      |  |  |

| TX only run peak current @TXpwr= -55 dBm     | 5 (5.0)             | mA   |  |  |

| Active Mode                                  |                     |      |  |  |

| RX only 'peak' current (Note2)               | 8.7 (8.7)           | mA   |  |  |

| Ultra Low Power Mode1 (Note 3)               |                     |      |  |  |

| Standby Doze                                 | 2.6                 | uA   |  |  |

| Ultra Low Power Mode2 (Note 4)               |                     |      |  |  |

| Deep Sleep (no RAM retention)                | 600 (Note 4)        | nA   |  |  |

| Active Mode Average current (Note 5)         |                     |      |  |  |

| Advertising Average Current draw             |                     |      |  |  |

| Max with advertising interval (min) 20 mS    | ~800                | uA   |  |  |

| Min with advertising interval (max) 10240 mS |                     |      |  |  |

| Connection Average Current draw              |                     |      |  |  |

| Max with connection interval (min) 7.5 mS    |                     | uA   |  |  |

| with connection interval 67.5 mS             | ~400                | uA   |  |  |

| Min with connection interval (max) 4000 mS   | ~2.6-4.1            | uA   |  |  |

Note 1: With VCC 3.3V with internal LDO ON (or with internal DCDC ON). If VCC reduces to 2.1V (operating range of DCDC, the peak current consumption would increase from 11.6mA to ~15.5mA for TX power setting of +4dBm.

*smart* BASIC runtime engine firmware v1.2.54.0(Jun2013) and subsequent versions, the internal DCDC convertor was switched off on recommendation from the chipset provider until future notice.

Hardware Integration Guide

- Note 2: Firmware version 1.1.50.0 (only) has an issue that TX PWR settings need to -40 dBm to produce -30 dBm and -65 dBm to produce -55 dBm.

- Note 3: BL600-Sx-02 and BL600-Sx-03: Standby Doze current 3.5uA typical. BL600-Sx-04: Standby Doze is 2.6uA typical. Standby Doze is entered automatically (when waitevent statement is encountered within a smartBASIC application script). In Standby Doze, all peripherals that are enabled stay on and may re-awaken the chip. Depending on active peripherals, current consumption ranges from ~2-4 μA to > 1 mA. See individual peripherals current consumption in tables in section Peripheral block current consumption 4.3. Since smart BASIC runtime engine firmware v1.3.57.0 (Sept. 2013) has added new function to detect GPIO change with no current consumption cost which means it is possible to close the UART and get to the 2.6-4 uA current consumption regime and yet still be able to detect for incoming data and be woken up so that the UART can be re-opened at expense of losing that first character.

- Note 4: In Deep Sleep, everything is disabled and the only wake-up sources are reset and changes on pins on which sense is enabled. The current consumption seen is ~600 nA typical in BL600-Sx-04. BL600-Sx-02 and BL600-Sx-03 this figure is ~1000nA.

\*\*smart\*\* BASIC runtime engine firmware v1.1.50.0 requires a hardware reset to come out of deep sleep. \*\*smart\*\* BASIC runtime engine firmware v1.2.54.0(Jun2013) release allows coming out from Deep Sleep to Standby Doze through GPIO signal through the reset vector. Deep Sleep mode is entered (with a command in \*\*smart\*\* BASIC application script).

- **Note 5:** Data taken with TX power 4 dBm and all peripherals off (UART OFF after radio event), slave latency of 0 (in a connection). Average current consumption depends on a number of factors [including TX power, VCC accuracy of 16 MHz and 32.768 kHz). With these factors fixed, the largest variable is the advertising or connection interval set.

## Advertising Interval range:

20 ms to 10240 ms in multiples of 0.625 ms for Advert type=ADV\_IND and ADV\_DIRECT\_IND. 100 ms to 10240 ms in multiples of 0.625 ms for Advert type=ADV\_SCAN\_IND and ADV\_NONCONN\_IND.

For advertising timeout, if the advert type is ADV\_DIRECT\_IND, then the timeout is limited to 1.28 seconds (1280 ms).

### For an advertising event:

- The minimum average current consumption is when the advertising interval is large 10240 mS (although this may cause long discover times (for the advertising event) by scanners

- The maximum average current consumption is when the advertising interval is small 20 mS

Other factors that are also related to average current consumption include the advertising payload bytes in each advertising packet and whether continuously advertising or periodically advertising.

#### **Connection Interval Range:**

7.5 ms to 4000 ms in multiples of 1.25 ms.

#### For a connection event:

- The minimum average current consumption is when the connection interval is large 4000 mS

- The maximum average current consumption is with the shortest connection interval of 7.5 ms; no slave latency.

© Copyright 2015 Laird. All Rights Reserved

Other factors that are also related to average current consumption include whether transmitting 6 packets per connection interval & each packet contains 20 bytes (which is the maximum for each packet) and an inaccurate 32 kHz master clock accuracy would increase the average current consumption.

# 4.2 Measured Peak Current Waveforms during Advertising and Connection

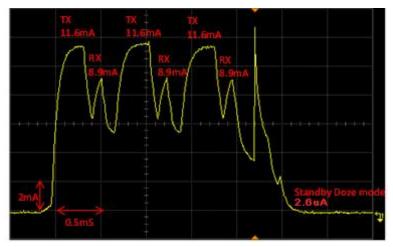

The following figures illustrate current waveforms observed as the BL600 module performs advertising and connection functionality.

Figure 3: Typical peak current consumption profile (with DCDC ON) during advertising in slave mode @ TX PWR +4dBm. UART is OFF. Last spike is DCDC being turned off.

Figure 4: Typical peak current consumption profile (with DCDC ON) during data connection event in slave mode @ TX PWR +4dBm. UART is ON. Last spike is DCDC being turned off

Hardware Integration Guide

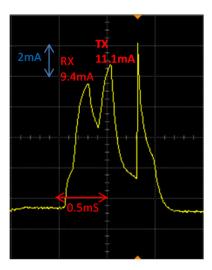

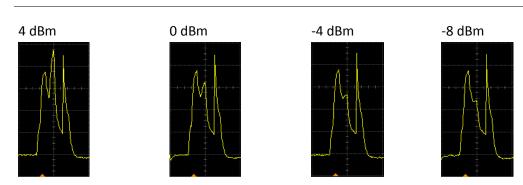

Figure 5: Typical peak current consumption profile (with DCDC ON) during advertising in slave mode versus TX PWR

## **Advertising (with Whisper Mode TX powers)**

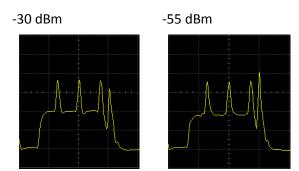

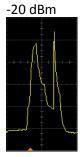

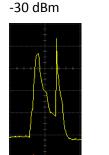

Figure 6: Typical peak current consumption profile (with DCDC ON) during advertising in slave mode with TX Whisper Mode TX PWR -30 dBm (TX Whisper Mode1) and -55 dBm (TX Whisper Mode2)

Note: In the above pictures, UART is ON. X-axis time (1 mS per square), Y-axis current (2 mA per square).

Hardware Integration Guide

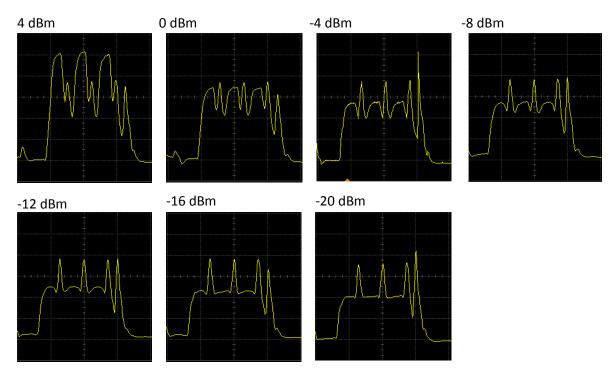

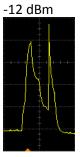

Figure 7: Typical peak current consumption profile (with DCDC ON) during connection event in slave mode versus TX PWR.

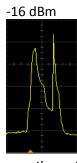

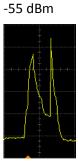

Figure 8: Typical peak current consumption profile during connection event in slave mode with TX Whisper mode TX PWR -30 dBm (TX Whisper Mode1) and -55 dBm (TX Whisper Mode2).

**Note:** In the above pictures, UART is ON. X-axis time (1 mS per square), Y-axis current (2 mA per square).

# 4.3 Peripheral Block Current Consumption

The values below are calculated for a typical operating voltage of 3 V.

**Table 10: UART Power Consumption**

| Parameter                     | Min | Тур | Max   | Unit |

|-------------------------------|-----|-----|-------|------|

| UART Run current @ 115200 bps |     | 220 |       | uA   |

| UART Run current @ 1200 bps   |     | 210 |       | uA   |

| UART Baud rate                | 1.2 |     | 115.2 | kbps |

**Table 11: SPI Power Consumption**

| Parameter                         | Min   | Тур | Max | Unit |

|-----------------------------------|-------|-----|-----|------|

| SPI Master Run current @ 125 kbps |       | 180 |     | uA   |

| SPI Master Run current @ 4 Mbps   |       | 200 |     | uA   |

| SPI bit rate                      | 0.125 |     | 4   | Mbps |

**Table 12: I2C Power Consumption**

| Parameter                  | Min | Тур | Max | Unit |

|----------------------------|-----|-----|-----|------|

| I2C Run current @ 100 kbps |     | 380 |     | uA   |

| I2C Run current @ 400 kbps |     | 400 |     | uA   |

| I2C Bit rate               | 100 |     | 400 | kbps |

Hardware Integration Guide

**Table 13: ADC Power Consumption**