## 7-Channel Configurable High Power PMIC

#### **FEATURES**

- Four Monolithic Synchronous Buck DC/DCs (1A/1A/500mA/500mA)

- Buck DC/DCs Can Be Paralleled to Deliver Up to 2× Current with a Single Inductor

- Independent 1A Boost and 1A Buck-Boost DC/DCs

- Dual String I<sup>2</sup>C Controlled 40V LED Driver

- I<sup>2</sup>C Programmable Output Voltage, Operating Mode, and Switch Node Slew Rate for All DC/DCs

- I<sup>2</sup>C Read Back of DC/DC, LED Driver, Fault Status

- I<sup>2</sup>C Slave Address Options: LTC3675 = 0001001X, LTC3675-1 = 0110100X

- Maskable Interrupts to Report DC/DC, V<sub>IN</sub> and Die Temperature Faults

- Pushbutton ON/OFF/RESET

- Always-On 25mA LDO

- Low Quiescent Current: 16µA (All DC/DCs Off)

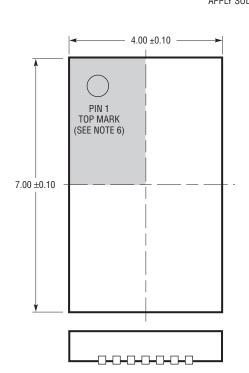

- 4mm × 7mm × 0.75mm 44-Lead QFN Package

### **APPLICATIONS**

- High Power (5W to 10W) Single Cell Li-Ion/Polymer Applications

- Portable Industrial Applications, Handy Terminals, Portable Instruments

- Multioutput Low Voltage Power Supplies

LT, LTC, LTM, Linear Technology, the Linear logo and Burst Mode are registered trademarks of Linear Technology Corporation and Hot Swap is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

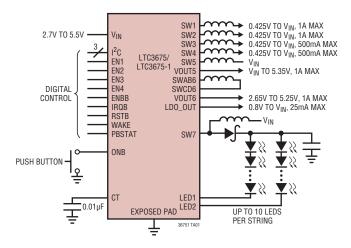

#### DESCRIPTION

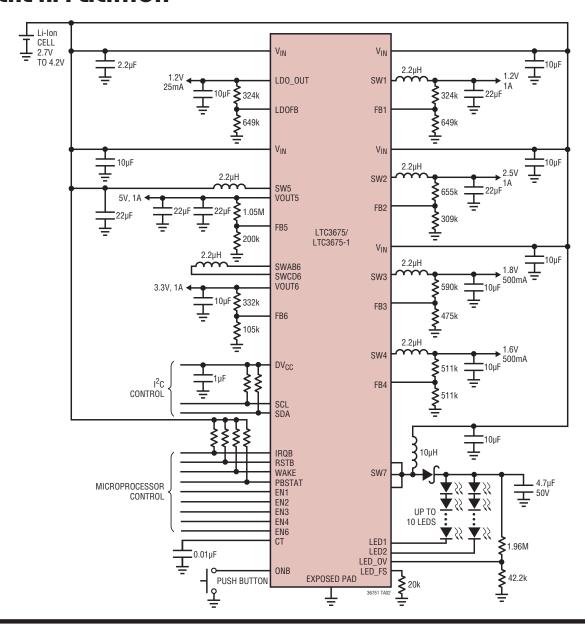

The LTC®3675/LTC3675-1 are a digitally programmable high efficiency multioutput power supplies plus dual string LED driver ICs optimized for high power single cell Li-Ion/Polymer applications. The DC/DCs consist of four synchronous buck converters (1A/1A/500mA/500mA), one synchronous boost DC/DC (1A), and one buck-boost DC/DC (1A) all powered from a 2.7V to 5.5V input. The 40V LED driver can regulate up to 25mA of current through two LED strings with up to 10 LEDs each. The LED driver may also be configured as a general purpose high voltage boost converter.

DC/DC enables, output voltages, switch slew rates and operating modes may all be independently programmed over  $I^2C$  or used in standalone mode via simple I/O and power-up defaults. The buck DC/DCs may be used independently or paralleled to achieve higher output currents with a shared inductor. LED enable, 60dB brightness control and up/down gradation are programmed using  $I^2C$ . Alarm levels for low  $V_{IN}$  and high die temperature may also be programmed via  $I^2C$  with a maskable interrupt output to monitor DC/DC and system faults.

Pushbutton ON/OFF/RESET control and a power-on reset output provide flexible and reliable power-up sequencing. The LTC3675/LTC3675-1 are available in a low profile (0.75mm), thermally enhanced 44-lead 4mm  $\times$  7mm QFN package.

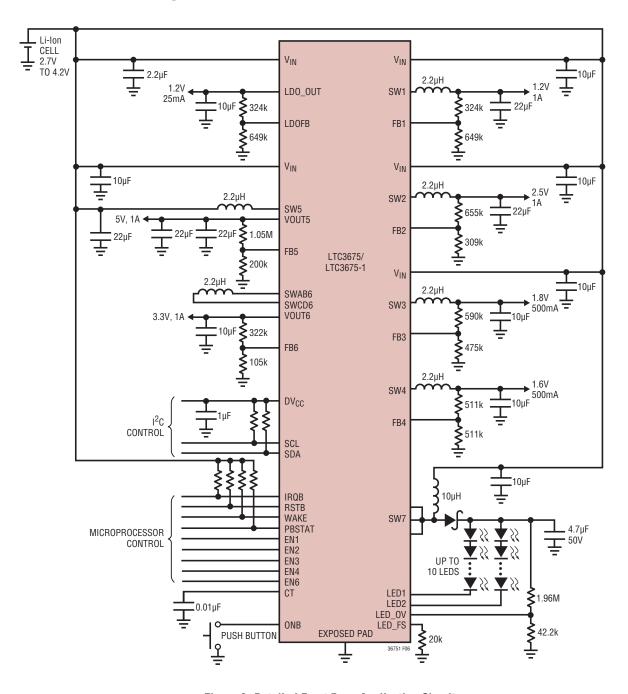

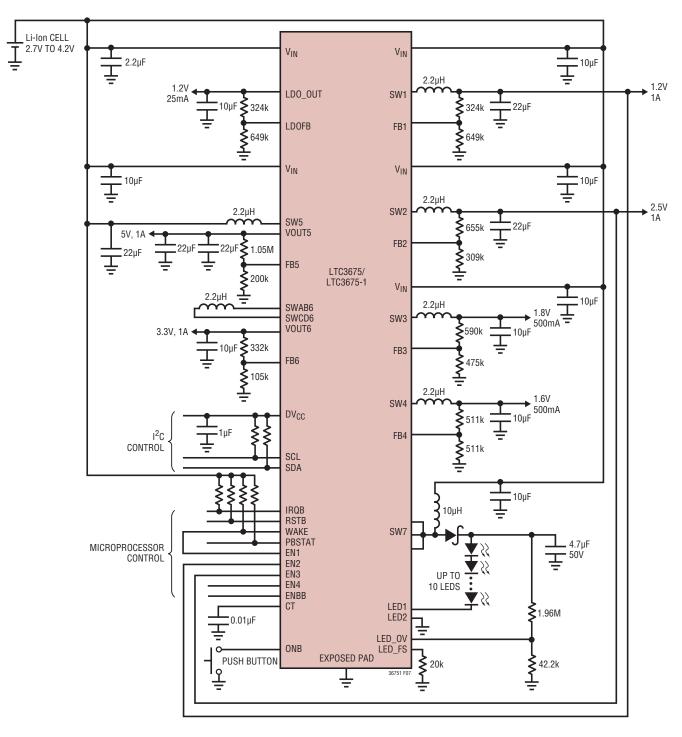

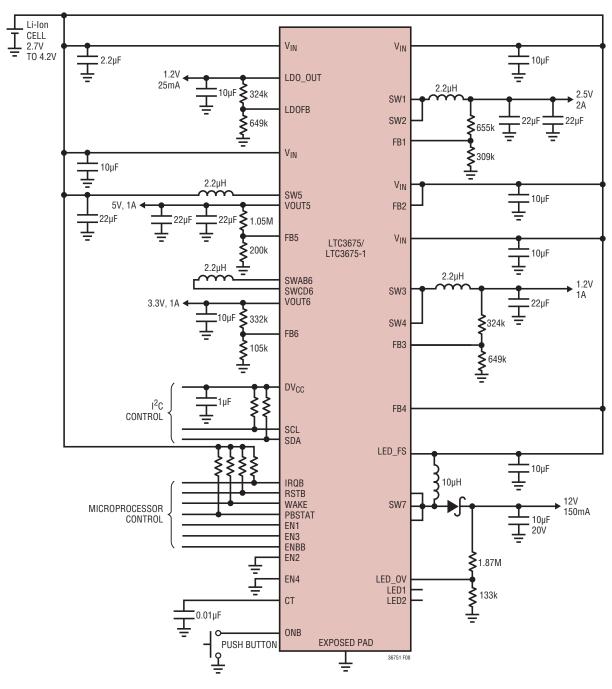

#### TYPICAL APPLICATION

## LTC3675/LTC3675-1

## TABLE OF CONTENTS

| Features                                                   |    |

|------------------------------------------------------------|----|

| Applications                                               | 1  |

| Typical Application                                        | 1  |

| Description                                                |    |

| Absolute Maximum Ratings                                   | 3  |

| Order Information                                          | 3  |

| Pin Configuration                                          | 3  |

| Electrical Characteristics                                 | 4  |

| Typical Performance Characteristics                        | 8  |

| Pin Functions                                              | 14 |

| Block Diagram                                              | 16 |

| Operation                                                  |    |

| Buck Switching Regulator                                   |    |

| Buck Regulators with Combined Power Stages                 |    |

| Boost Switching Regulator                                  |    |

| Buck-Boost Switching Regulator                             |    |

| LED Driver                                                 |    |

| Pushbutton Interface and Power-Up Power-Down Sequencing    |    |

| Power-Up and Power-Down via Pushbutton                     | 19 |

| Power-Up and Power-Down via Enable Pin or I <sup>2</sup> C | 21 |

| LED Current Programming                                    |    |

| I <sup>2</sup> C Interface                                 | 21 |

| Error Condition Reporting via                              |    |

| RSTB and IRQB Pins                                         |    |

| Undervoltage and Overtemperature Functionality             |    |

| Applications Information                                   |    |

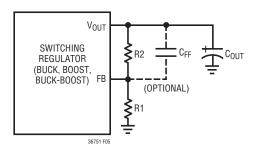

| Switching Regulator Output Voltage and Feedback Network    |    |

| Buck Regulators                                            |    |

| Combined Buck Regulators                                   |    |

| Boost Regulator                                            |    |

| Buck-Boost Regulator                                       |    |

| LED Driver                                                 | 28 |

| Operating the LED Driver As a High Voltage Boost Regulator |    |

| Input and Output Decoupling Capacitor Selection            |    |

| Choosing the C <sub>T</sub> Capacitor                      |    |

| Programming the UVOT Register                              |    |

| Programming the RSTB and IRQB Mask Registers               |    |

| Status Byte Read Back                                      |    |

| PCB Considerations                                         |    |

| Typical Applications                                       |    |

| Package Description                                        |    |

| Revision History                                           |    |

| Typical Application                                        |    |

| Doloted Doute                                              |    |

#### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

V<sub>IN</sub>, V<sub>OUT5</sub>, V<sub>OUT6</sub>, FB1-6, LED\_OV, EN1-4, ENBB, LED\_ FS, CT, WAKE, PBSTAT, IRQB, RSTB, ONB, DVCC. SW5......-0.3V to 6V (Static) LDO\_OUT, LDOFB...-0.3V to Lesser of  $(V_{IN} + 0.3V)$  or 6VSCL, SDA ......... -0.3V to Lesser of (DV<sub>CC</sub> + 0.3V) or 6V SW1, SW2, SW3, SW4, SWAB6 ...... -0.3V to Lesser of  $(V_{IN} + 0.3V)$  or 6VSWCD6 .....-0.3V to Lesser of  $(V_{OUT6} + 0.3V)$  or 6V SW7......-0.3V to 45V I<sub>SW1</sub>, I<sub>SW2</sub> .......1.4A I<sub>SW5</sub>, I<sub>SWAB6</sub>, I<sub>SWCD6</sub>......2.4A I<sub>SW7</sub> .......2A Operating Junction Temperature Range (Notes 2, 3) ......–40°C to 125°C Storage Temperature Range ......-65°C to 125°C

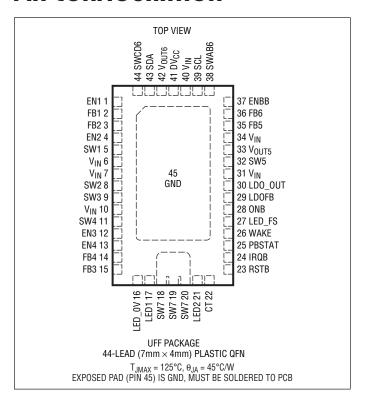

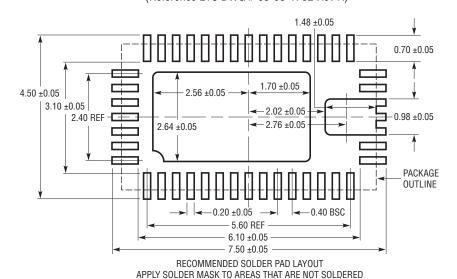

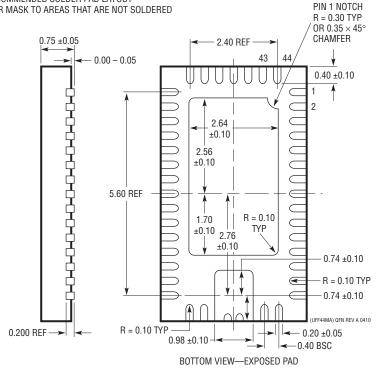

#### PIN CONFIGURATION

#### ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|---------------------|--------------|---------------------------------|-------------------|

| LTC3675EUFF#PBF   | LTC3675EUFF#TRPBF   | 3675         | 44-Lead (7mm × 4mm) Plastic QFN | -40°C to 125°C    |

| LTC3675EUFF-1#PBF | LTC3675EUFF-1#TRPBF | 36751        | 44-Lead (7mm × 4mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 3.6V$ . (Note 2)

| SYMBOL                    | PARAMETER                                                                           | CONDITIONS                                                                                                           |   | MIN  | TYP                  | MAX       | UNITS          |

|---------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---|------|----------------------|-----------|----------------|

| V <sub>IN</sub>           | Input Supply Range                                                                  |                                                                                                                      | • | 2.7  |                      | 5.5       | V              |

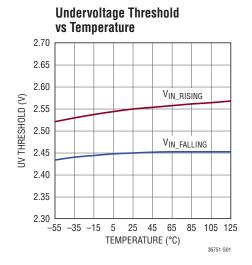

| V <sub>IN_FALLING</sub>   | Falling Undervoltage Threshold                                                      |                                                                                                                      | • | 2.35 | 2.45                 | 2.55      | V              |

| V <sub>IN_RISING</sub>    | Rising Undervoltage Threshold                                                       |                                                                                                                      | • | 2.45 | 2.55                 | 2.65      | V              |

| V <sub>IN_WARN</sub>      | Falling Undervoltage Warning Threshold                                              | UV[2], UV[1], UV[0] = 000                                                                                            |   |      | 2.7                  |           | V              |

|                           |                                                                                     | UV[2], UV[1], UV[0] = 001                                                                                            |   |      | 2.8                  |           | V              |

|                           |                                                                                     | UV[2], UV[1], UV[0] = 010                                                                                            |   |      | 2.9                  |           | V              |

|                           |                                                                                     | UV[2], UV[1], UV[0] = 011                                                                                            |   |      | 3.0                  |           | V              |

|                           |                                                                                     | UV[2], UV[1], UV[0] = 100                                                                                            |   |      | 3.1                  |           | V              |

|                           |                                                                                     | UV[2], UV[1], UV[0] = 101                                                                                            |   |      | 3.2                  |           | V              |

|                           |                                                                                     | UV[2], UV[1], UV[0] = 110                                                                                            |   |      | 3.3                  |           | V              |

|                           |                                                                                     | UV[2], UV[1], UV[0] = 111                                                                                            |   |      | 3.4                  |           | V              |

| V <sub>IN_HYS</sub>       | V <sub>IN</sub> Undervoltage Warning Hysteresis                                     |                                                                                                                      |   |      | 50                   |           | mV             |

| V <sub>IN_WARN(LSB)</sub> | Undervoltage Warning Threshold Step Size                                            |                                                                                                                      | • | 85   | 100                  | 115       | mV             |

| OT                        | Overtemperature Shutdown                                                            |                                                                                                                      |   |      | 150                  |           | °C             |

| OT_WARN                   | Overtemperature Warning Threshold; Die<br>Temperature Below OT that Causes IRQB = 0 | OT[1], OT[0] = 00<br>OT[1], OT[0] = 01<br>OT[1], OT[0] = 10<br>OT[1], OT[0] = 11                                     |   |      | 10<br>20<br>30<br>40 |           | 0°<br>0°<br>0° |

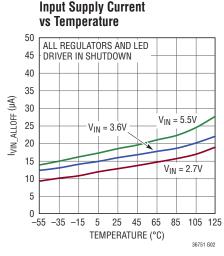

| I <sub>VIN_</sub> ALLOFF  | Input Supply Current                                                                | All Switching Regulators and LED Driver in Shutdown, ONB = HIGH; Sum of All V <sub>IN</sub> Currents                 |   |      | 16                   | 28        | μА             |

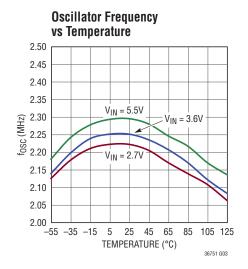

| f <sub>OSC</sub>          | Voltage Regulator Switching Frequency                                               | All Voltage Regulators                                                                                               | • | 1.8  | 2.25                 | 2.7       | MHz            |

| V <sub>PGOOD(FALL)</sub>  | Falling PGOOD Threshold Voltage                                                     | Full-Scale (1,1,1,1) Reference Voltage                                                                               | • | 88   | 92                   | 96        | %              |

| V <sub>PGOOD(HYS)</sub>   | PGOOD Hysteresis                                                                    | All Regulators Except LED Driver                                                                                     |   |      | 1                    |           | %              |

| 1A Buck Regula            | ator (Buck Regulators 1 and 2)                                                      | ,                                                                                                                    |   |      |                      |           |                |

| I <sub>VIN1,2</sub>       | Pulse-Skipping Input Current<br>Burst Mode® Operation Input Current                 | V <sub>FB1</sub> = V <sub>FB2</sub> = 0.85V (Notes 4, 5)<br>V <sub>FB1</sub> = V <sub>FB2</sub> = 0.85V (Notes 4, 5) |   |      | 105<br>20            | 200<br>50 | μA<br>μA       |

| I <sub>FWD1,2</sub>       | PMOS Current Limit                                                                  | (Note 6)                                                                                                             |   | 2.25 | 2.8                  | 3.35      | А              |

| V <sub>FB1,2(HIGH)</sub>  | Feedback Regulation Voltage                                                         | Pulse-Skipping Mode Full-Scale (1,1,1,1)                                                                             | • | 780  | 800                  | 820       | mV             |

| V <sub>FB1,2(LOW)</sub>   | Feedback Regulation Voltage                                                         | Pulse-Skipping Mode Full-Scale (0,0,0,0)                                                                             | • | 405  | 425                  | 445       | mV             |

| V <sub>LSB1,2</sub>       | FB1, FB2 Regulation Voltage Step Size                                               |                                                                                                                      |   |      | 25                   |           | mV             |

| I <sub>FB12</sub>         | Feedback Leakage Current                                                            | $V_{FB1} = V_{FB2} = 0.85V$                                                                                          |   | -50  |                      | 50        | nA             |

| D <sub>MAX1,2</sub>       | Maximum Duty Cycle                                                                  | $V_{FB1} = V_{FB2} = 0V$                                                                                             | • | 100  |                      |           | %              |

| R <sub>PMOS1,2</sub>      | PMOS On-Resistance                                                                  | $I_{SW1} = I_{SW2} = 100 \text{mA}$                                                                                  |   |      | 265                  |           | mΩ             |

| R <sub>NMOS1,2</sub>      | NMOS On-Resistance                                                                  | $I_{SW1} = I_{SW2} = -100 \text{mA}$                                                                                 |   |      | 280                  |           | mΩ             |

| I <sub>LEAKP1,2</sub>     | PMOS Leakage Current                                                                | EN1 = EN2 = 0                                                                                                        |   | -2   |                      | 2         | μА             |

| I <sub>LEAKN1,2</sub>     | NMOS Leakage Current                                                                | EN1 = EN2 = 0                                                                                                        |   | -2   |                      | 2         | μА             |

| R <sub>SWPD1,2</sub>      | Output Pull-Down Resistance in Shutdown                                             | EN1 = EN2 = 0 (I <sup>2</sup> C Bit Set)                                                                             |   |      | 10                   |           | kΩ             |

| t <sub>SS1,2</sub>        | Soft-Start Time                                                                     |                                                                                                                      |   |      | 500                  |           | μs             |

| 500mA Buck Re             | egulator (Buck Regulators 3 and 4)                                                  |                                                                                                                      |   |      |                      |           |                |

| I <sub>VIN3,4</sub>       | Pulse-Skipping Input Current<br>Burst Mode Operation Input Current                  | V <sub>FB3</sub> = V <sub>FB4</sub> = 0.85V (Notes 4, 5)<br>V <sub>FB3</sub> = V <sub>FB4</sub> = 0.85V (Notes 4, 5) |   |      | 105<br>20            | 200<br>50 | μΑ<br>μΑ       |

| I <sub>FWD3,4</sub>       | PMOS Current Limit                                                                  | (Note 6)                                                                                                             |   | 0.75 | 1.2                  | 1.65      | A              |

/ LINEAR

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 3.6V$ . (Note 2)

| SYMBOL                   | PARAMETER                               | CONDITIONS                                                                     |   | MIN  | TYP       | MAX       | UNITS    |

|--------------------------|-----------------------------------------|--------------------------------------------------------------------------------|---|------|-----------|-----------|----------|

| V <sub>FB3,4(HIGH)</sub> | Feedback Regulation Voltage             | Pulse-Skipping Mode Full-Scale (1,1,1,1)                                       | • | 780  | 800       | 820       | mV       |

| V <sub>FB3,4(LOW)</sub>  | Feedback Regulation Voltage             | Pulse-Skipping Mode Full-Scale (0,0,0,0)                                       | • | 405  | 425       | 445       | mV       |

| V <sub>LSB3,4</sub>      | FB3, FB4 Regulation Voltage Step Size   |                                                                                |   |      | 25        |           | mV       |

| I <sub>FB3,4</sub>       | Feedback Leakage Current                | $V_{FB3} = V_{FB4} = 0.85V$                                                    |   | -50  |           | 50        | nA       |

| D <sub>MAX3,4</sub>      | Maximum Duty Cycle                      | $V_{FB3} = V_{FB4} = 0V$                                                       | • | 100  |           |           | %        |

| R <sub>PMOS3,4</sub>     | PMOS On-Resistance                      | I <sub>SW3</sub> = I <sub>SW4</sub> = 100mA                                    |   |      | 500       |           | mΩ       |

| R <sub>NMOS3,4</sub>     | NMOS On-Resistance                      | $I_{SW3} = I_{SW4} = -100 \text{mA}$                                           |   |      | 510       |           | mΩ       |

| I <sub>LEAKP3,4</sub>    | PMOS Leakage Current                    | EN3 = EN4 = 0                                                                  |   | -1   |           | 1         | μА       |

| I <sub>LEAKN3,4</sub>    | NMOS Leakage Current                    | EN3 = EN4 = 0                                                                  |   | -1   |           | 1         | μА       |

| R <sub>SWPD3,4</sub>     | Output Pull-Down Resistance in Shutdown | $EN3 = EN4 = 0$ ( $I^2C$ Bit Set)                                              |   |      | 10        |           | kΩ       |

| t <sub>SS3,4</sub>       | Soft-Start Time                         |                                                                                |   |      | 500       |           | μs       |

| Buck Regulato            | ors Combined                            |                                                                                |   |      |           |           |          |

| I <sub>FWD1+2</sub>      | PMOS Current Limit                      | FB2 = V <sub>IN</sub> (Note 6)                                                 |   |      | 5.6       |           | А        |

| I <sub>FWD2+3</sub>      | PMOS Current Limit                      | FB3 = V <sub>IN</sub> (Note 6)                                                 |   |      | 4         |           | А        |

| I <sub>FWD3+4</sub>      | PMOS Current Limit                      | FB4 = V <sub>IN</sub> (Note 6)                                                 |   |      | 2.4       |           | А        |

| 1A Boost Regu            | ılator                                  |                                                                                |   |      |           |           |          |

| I <sub>VIN5</sub>        | PWM Mode<br>Burst Mode Operation        | V <sub>FB5</sub> = 0.85V (Notes 4, 5)<br>V <sub>FB5</sub> = 0.85V (Notes 4, 5) |   |      | 150<br>35 | 300<br>60 | μA<br>μA |

| V <sub>OUT5(MAX)</sub>   | Maximum Regulated Output Voltage        |                                                                                |   | 5.35 | 5.55      | 5.75      | V        |

| I <sub>FWD5</sub>        | Forward Current Limit                   | (Note 6)                                                                       |   | 2.5  | 3.15      | 3.9       | А        |

| V <sub>FB5(HIGH)</sub>   | Feedback Regulation Voltage             | PWM Mode Full-Scale (1,1,1,1)                                                  | • | 780  | 800       | 820       | mV       |

| V <sub>FB5(LOW)</sub>    | Feedback Regulation Voltage             | PWM Mode Full-Scale (0,0,0,0)                                                  | • | 405  | 425       | 445       | mV       |

| $V_{LSB5}$               | FB5 Regulation Voltage Step Size        |                                                                                |   |      | 25        |           | mV       |

| I <sub>FB5</sub>         | Feedback Leakage Current                | V <sub>FB5</sub> = 0.85V                                                       |   | -50  |           | 50        | nA       |

| DC <sub>MAX5</sub>       | Maximum Duty Cycle                      | NMOS Switch                                                                    |   |      | 90        |           | %        |

| R <sub>PMOS5</sub>       | PMOS On-Resistance                      |                                                                                |   |      | 260       |           | mΩ       |

| R <sub>NMOS5</sub>       | NMOS On-Resistance                      |                                                                                |   |      | 275       |           | mΩ       |

| I <sub>LEAKP</sub>       | PMOS Switch Leakage Current             |                                                                                |   | -2   |           | 2         | μА       |

| I <sub>LEAKN</sub>       | NMOS Switch Leakage Current             |                                                                                |   | -2   |           | 2         | μA       |

| R <sub>OUTPD5</sub>      | Output Pull-Down Resistance in Shutdown | Boost Regulator Off                                                            |   |      | 10        |           | kΩ       |

| t <sub>SS5</sub>         | Soft-Start Time                         |                                                                                |   |      | 500       |           | μs       |

| 1A Buck-Boost            | t Regulator                             |                                                                                |   |      |           |           |          |

| I <sub>VIN6</sub>        | PWM Mode<br>Burst Mode Operation        | V <sub>FB6</sub> = 0.85V (Note 4, 5)<br>V <sub>FB6</sub> = 0.85V (Note 4, 5)   |   |      | 220<br>20 | 400<br>40 | μA<br>μA |

| V <sub>OUT6(LOW)</sub>   | Minimum Regulated Output Voltage        |                                                                                |   |      | 2.65      | 2.8       | V        |

| V <sub>OUT6(HIGH)</sub>  | Maximum Regulated Output Voltage        |                                                                                |   | 5.25 | 5.65      |           | V        |

| I <sub>FWD6</sub>        | Forward Current Limit                   | PWM Mode (Note 6)                                                              |   | 2.1  | 2.65      | 3.2       | А        |

| I <sub>PEAK6</sub>       | Peak Current Limit                      | Burst Mode Operation (Note 6)                                                  |   | 200  | 275       | 350       | mA       |

| I <sub>ZER06</sub>       | Zero Current Limit                      | Burst Mode Operation                                                           |   | -30  | 0         | 30        | mA       |

| V <sub>FB6(HIGH)</sub>   | Feedback Regulation Voltage             | PWM Mode Full-Scale (1,1,1,1)                                                  | • | 780  | 800       | 820       | mV       |

| V <sub>FB6(LOW)</sub>    | Feedback Regulation Voltage             | PWM Mode Full-Scale (0,0,0,0)                                                  | • | 405  | 425       | 445       | mV       |

| V <sub>LSB6</sub>        | FB6 Regulation Voltage Step Size        | - (-1-1-1-1)                                                                   |   |      | 25        |           | mV       |

|                          | 1 0                                     | 1                                                                              |   |      |           |           |          |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . $V_{IN} = 3.6 \,^{\circ}\text{C}$ . (Note 2)

| SYMBOL                      | PARAMETER                                     | CONDITIONS                                                                                   |   | MIN                            | TYP        | MAX        | UNITS             |

|-----------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------|---|--------------------------------|------------|------------|-------------------|

| I <sub>FB6</sub>            | Feedback Leakage Current                      | V <sub>FB6</sub> = 0.85V                                                                     |   | -50                            |            | 50         | nA                |

| DC6 <sub>BUCK(MAX)</sub>    | Maximum Buck Duty Cycle                       | Duty Cycle of PMOS Switch A                                                                  | • | 100                            |            |            | %                 |

| DC6 <sub>BOOST(MAX)</sub>   | Maximum Boost Duty Cycle                      | Duty Cycle of NMOS Switch C                                                                  |   |                                | 75         |            | %                 |

| R <sub>PMOS6</sub>          | PMOS On-Resistance                            | Switches A and D                                                                             |   |                                | 260        |            | mΩ                |

| R <sub>NMOS6</sub>          | NMOS On-Resistance                            | Switches B and C                                                                             |   |                                | 275        |            | mΩ                |

| I <sub>LEAKP</sub>          | PMOS Switch Leakage Current                   |                                                                                              |   | -2                             |            | 2          | μА                |

| I <sub>LEAKN</sub>          | NMOS Switch Leakage Current                   |                                                                                              |   | -2                             |            | 2          | μА                |

| $\overline{t_{SS}}$         | Soft-Start Time                               |                                                                                              |   |                                | 500        |            | μs                |

| R <sub>OUTPD6</sub>         | Output Pull-Down Resistance in Shutdown       | ENBB = 0                                                                                     |   |                                | 10         |            | kΩ                |

| LED Driver; R <sub>LE</sub> | D FS = 20kΩ                                   |                                                                                              |   |                                |            |            |                   |

| I <sub>VIN7</sub>           | Input Current (MODE0 = MODE1 = 0)             | LED_OV = 0.85V (Notes 4, 5)                                                                  |   |                                | 700        | 1000       | μА                |

| V <sub>LED_OV</sub>         | LED Overvoltage Threshold<br>Feedback Voltage | Operating in LED Mode<br>Operating in Boost Mode                                             | • | 805<br>770                     | 825<br>800 | 845<br>830 | mV<br>mV          |

| V <sub>LED_FS</sub>         | LED Full-Scale Voltage                        |                                                                                              | • | 775                            | 800        | 825        | mV                |

| V <sub>LED1,2</sub>         | LED Pin Regulation Voltage                    | (Note 7)                                                                                     |   |                                | 300        |            | mV                |

| V <sub>LED1,2_CLMP</sub>    | LED Regulation Voltage Clamp                  |                                                                                              | • | 6.0                            |            | 8.3        | V                 |

| I <sub>LIM7</sub>           | Maximum Current Limit                         | (Note 6)                                                                                     |   | 1.6                            | 1.85       | 2.15       | А                 |

| I <sub>LED_FS</sub>         | LED Full-Scale Current                        |                                                                                              | • | 23.25                          | 25.0       | 26.75      | mA                |

| I <sub>LED_2FS</sub>        | LED Full Current High Current Mode            |                                                                                              | • | 46.5                           | 50         | 53.5       | mA                |

| I <sub>LED_MATCH</sub>      | LED1 and LED2 Current Matching at Full-Scale  | $\frac{\frac{ I_{LED1} - I_{LED2} }{\left(\frac{I_{LED1} + I_{LED2}}{2}\right)} \bullet 100$ | • |                                |            | 1          | %                 |

| I <sub>LED_LSB</sub>        | LED Current LSB                               |                                                                                              |   |                                | 98         |            | μA                |

| R <sub>NMOS7</sub>          | NMOS On-Resistance                            |                                                                                              |   |                                | 300        |            | mΩ                |

| I <sub>LEAK_NMOS7</sub>     | NMOS Switch Leakage                           | V <sub>SW7</sub> = 5.5V                                                                      |   | -1                             |            | 1          | μA                |

| F <sub>LEDOSC</sub>         | Oscillator Frequency                          |                                                                                              | • | 450                            | 562.5      | 675        | kHz               |

| DC <sub>MAX7</sub>          | Maximum Duty Cycle                            | NMOS Switch                                                                                  |   |                                | 97         |            | %                 |

| 25mA Always-0               | In LDO                                        |                                                                                              |   |                                |            |            |                   |

| $V_{LDOFB}$                 | Feedback Regulation Voltage                   |                                                                                              | • | 780                            | 800        | 820        | mV                |

| R <sub>D0</sub>             | Dropout Resistance                            |                                                                                              |   |                                | 12         |            | Ω                 |

| I <sup>2</sup> C Port       |                                               |                                                                                              |   |                                |            |            |                   |

| DV <sub>CC</sub>            | Input Supply Voltage                          |                                                                                              | • | 1.6                            |            | 5.5        | V                 |

| I <sub>DVCC</sub>           | Input Supply Current                          | SCL/SDA= 0kHz                                                                                |   |                                | 0.3        | 1          | μА                |

| DV <sub>CC_UVLO</sub>       | DV <sub>CC</sub> UVLO                         |                                                                                              |   |                                | 1          |            | V                 |

| ADDRESS                     | I <sup>2</sup> C Address                      | LTC3675<br>LTC3675-1                                                                         | • | 0001001[R/WB]<br>0110100[R/WB] |            | B]<br>B]   |                   |

| $\overline{V_{\text{IH}}}$  | Input High Voltage                            | SDA/SCL                                                                                      |   |                                | 70         |            | %DV <sub>CC</sub> |

| V <sub>IL</sub>             | Input Low Voltage                             | SDA/SCL                                                                                      |   |                                | 30         |            | %DV <sub>CC</sub> |

| I <sub>IH</sub>             | Input High Current                            | SDA/SCL                                                                                      |   | -1                             | 0          | 1          | μА                |

| I <sub>IL</sub>             | Input Low Current                             | SDA/SCL                                                                                      |   | -1                             | 0          | 1          | μА                |

| V <sub>OL_SDA</sub>         | SDA Output Low Voltage                        | I <sub>SDA</sub> = 3mA                                                                       |   |                                |            | 0.4        | V                 |

| f <sub>SCL</sub>            | Clock Operating Frequency                     |                                                                                              |   |                                |            | 400        | kHz               |

|                             |                                               | 1                                                                                            |   |                                |            |            | 36751fc           |

/ LINEAR

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 3.6V$ . (Note 2)

| SYMBOL                 | PARAMETER                                          | CONDITIONS                                        |   | MIN                  | TYP | MAX  | UNITS |

|------------------------|----------------------------------------------------|---------------------------------------------------|---|----------------------|-----|------|-------|

| t <sub>BUF</sub>       | Bus Free Time Between Stop and Start<br>Condition  |                                                   |   | 1.3                  |     |      | μs    |

| t <sub>HD_SDA</sub>    | Hold Time After Repeated Start Condition           |                                                   |   | 0.6                  |     |      | μs    |

| t <sub>SU_STA</sub>    | Repeated Start Condition Set-Up Time               |                                                   |   | 0.6                  |     |      | μs    |

| t <sub>SU_STO</sub>    | Stop Condition Set-Up Time                         |                                                   |   | 0.6                  |     |      | μs    |

| t <sub>HD_DAT(0)</sub> | Data Hold Time Output                              |                                                   |   | 0                    |     | 900  | ns    |

| t <sub>HD_DAT(I)</sub> | Data Hold Time Input                               |                                                   |   | 0                    |     |      | ns    |

| t <sub>SU_DAT</sub>    | Data Set-Up Time                                   |                                                   |   | 100                  |     |      | ns    |

| t <sub>LOW</sub>       | SCL Clock Low Period                               |                                                   |   | 1.3                  |     |      | μs    |

| t <sub>HIGH</sub>      | SCL Clock High Period                              |                                                   |   | 0.6                  |     |      | μs    |

| t <sub>f</sub>         | Clock/Data Fall Time                               | C <sub>B</sub> = Capacitance of One Bus Line (pF) |   | 20+0.1C <sub>B</sub> |     | 300  | ns    |

| t <sub>r</sub>         | Clock/Data Rise Time                               | C <sub>B</sub> = Capacitance of One Bus Line (pF) |   | 20+0.1C <sub>B</sub> |     | 300  | ns    |

| t <sub>SP</sub>        | Input Spike Suppression Pulse Width                |                                                   |   |                      |     | 50   | ns    |

| Interface Logi         | c Pins (PBSTAT, WAKE, RSTB, IRQB, ONB)             |                                                   |   |                      |     |      |       |

| I <sub>LK(HIGH)</sub>  | Output High Leakage Current                        | 3.6V at Pin                                       |   | -1                   |     | 1    | μА    |

| V <sub>OL</sub>        | Output Low Voltage                                 | 3mA into Pin                                      |   |                      | 100 | 400  | mV    |

| V <sub>ONB(HIGH)</sub> | ONB High Threshold                                 |                                                   |   |                      | 800 | 1200 | mV    |

| V <sub>ONB(LOW)</sub>  | ONB Low Threshold                                  |                                                   |   | 400                  | 700 |      | mV    |

| Interface Logi         | c Pins (EN1, EN2, EN3, EN4, ENBB)                  |                                                   |   |                      |     |      |       |

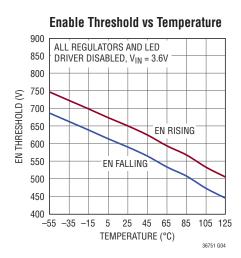

| V <sub>HI_ALLOFF</sub> | Enable Rising Threshold                            | All Regulators and LED Driver Disabled            | • | 400                  | 650 | 1200 | mV    |

| V <sub>EN_HYS</sub>    | Enable Falling Hysteresis                          |                                                   |   |                      | 60  |      | mV    |

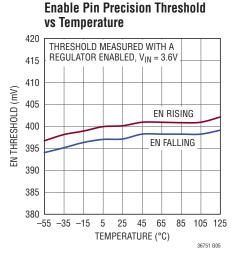

| $V_{HI}$               | Enable Rising Threshold                            | At Least One Regulator/LED Driver Enabled         | • | 380                  | 400 | 420  | mV    |

| I <sub>EN</sub>        | Enable Pin Leakage Current                         | EN = 3.6V                                         |   | -1                   |     | 1    | μА    |

| Pushbutton Pa          | rameters; CT = 0.01μF                              |                                                   |   |                      |     |      |       |

| t <sub>ONB_LO</sub>    | ONB Low Time to PBSTAT Low                         | WAKE High                                         |   | 28                   | 50  | 72   | ms    |

| t <sub>onb_wake</sub>  | ONB Low Time to WAKE High                          |                                                   |   | 280                  | 400 | 520  | ms    |

| t <sub>ONB_HR</sub>    | ONB Low to Hard Reset                              |                                                   |   | 3.5                  | 5   | 6.5  | sec   |

| t <sub>HR</sub>        | Time for Which All Enabled Regulators are Disabled |                                                   |   | 0.7                  | 1   | 1.3  | sec   |

| t <sub>PBSTAT_PW</sub> | PBSTAT Minimum Pulse Width                         |                                                   |   | 28                   | 50  | 72   | ms    |

| t <sub>WAKE_ON</sub>   | WAKE High Time                                     |                                                   |   | 3.5                  | 5   | 6.5  | sec   |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3675/LTC3675-1 are tested under pulsed load conditions such that  $T_A \approx T_J$ . The LTC3675/LTC3675-1 are guaranteed to meet performance specifications from 0°C to 125°C. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

**Note 3:** The LTC3675/LTC3675-1 include overtemperature protection which protects the device during momentary overload conditions. Junction

temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 4:** Static current, switches not switching. Actual current may be higher due to gate charge losses at the switching frequency.

**Note 5:** Currents measured at a specific  $V_{IN}$  pin. Buck 1 ( $V_{IN}$ , Pin 6); Buck 2 ( $V_{IN}$ , Pin 7); Buck 3 and Buck 4 ( $V_{IN}$ , Pin 10); Boost and Buck Boost ( $V_{IN}$ , Pin 34); LED driver ( $V_{IN}$ , Pin 31).

**Note 6:** The current limit features of this part are intended to protect the IC from short term or intermittent fault conditions. Continuous operation above the maximum specified pin current rating may result in device degradation over time.

**Note 7:** With dual string operation, the LED pin with the lower voltage sets the regulation point.

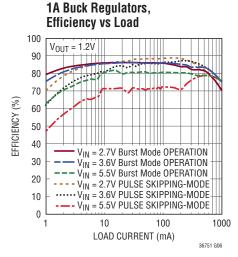

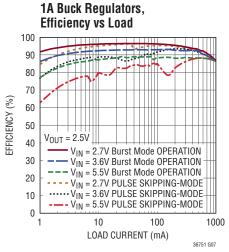

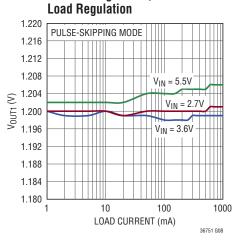

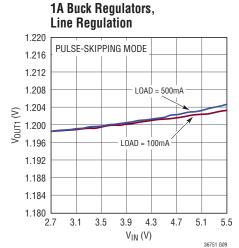

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

1A Buck Regulators,

### TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

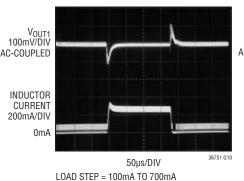

1A Buck Regulators, Transient Response (Pulse-Skipping Mode)

1A Buck Regulators, Transient Response (Burst Mode Operation)

LOAD STEP = 100mA TO 700mA V<sub>IN</sub> = 3.6V, V<sub>OUT1</sub> = 1.2V

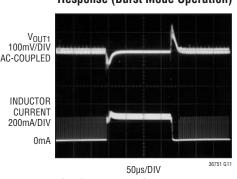

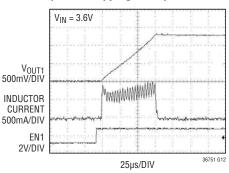

1A Buck Regulators, No Load Start-Up Transient (Pulse-Skipping Mode)

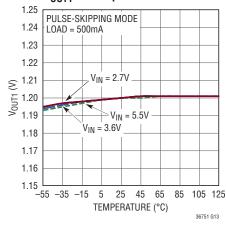

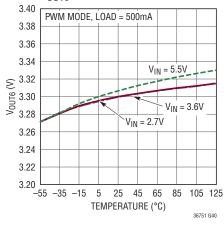

1A Buck Regulators, V<sub>OUT1</sub> vs Temperature

$V_{IN} = 3.6V, V_{OUT1} = 1.2V$

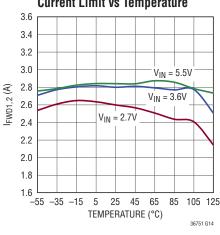

1A Buck Regulators, PMOS Current Limit vs Temperature

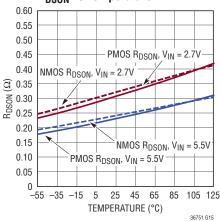

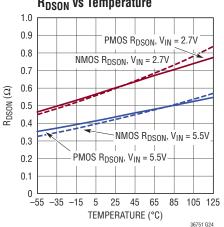

1A Buck Regulators, Switch R<sub>DSON</sub> vs Temperature

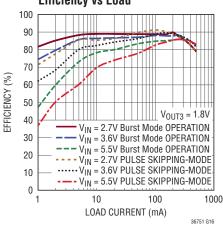

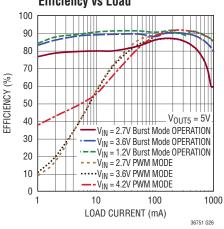

500mA Buck Regulators, Efficiency vs Load

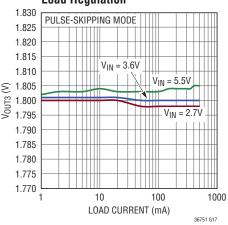

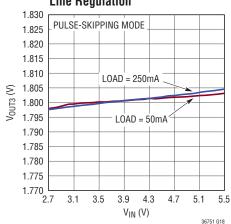

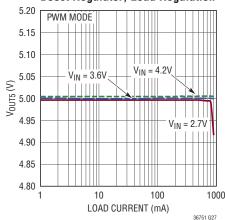

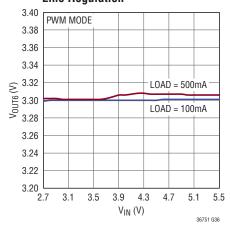

500mA Buck Regulators, Load Regulation

500mA Buck Regulators, Line Regulation

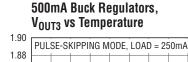

### TYPICAL PERFORMANCE CHARACTERISTICS TA = 25°C, unless otherwise noted.

500mA Buck Regulators No Load **500mA Buck Regulators Transient 500mA Buck Regulators Transient** Start-Up Transient Response (Pulse-Skipping Mode) Response (Burst Mode Operation) (Pulse-Skipping Mode)  $V_{IN} = 3.6V$  $V_{OUT3}$  $V_{OUT3}$ 100mV/DIV 100mV/DIV AC-COUPLED AC-COUPLED V<sub>OUT3</sub> 500mV/DIV INDUCTOR CURRENT INDUCTOR INDUCTOR 500mA/DIV CURRENT CURRENT 100mA/DIV 100mA/DIV ΕN 2V/DIV 36751 G19 36751 G20 36751 G21 50µs/DIV 50µs/DIV 25µs/DIV LOAD STEP = 50mA to 300mA LOAD STEP = 50mA to 300mA

$V_{IN} = 3.6V, V_{OUT3} = 1.8V$

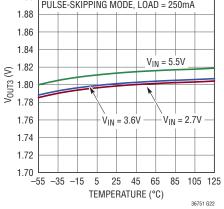

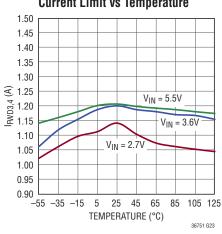

500mA Buck Regulators, PMOS Current Limit vs Temperature

$V_{IN} = 3.6V, V_{OUT3} = 1.8V$

500mA Buck Regulators, Switch R<sub>DSON</sub> vs Temperature

Ganged Buck Regulators 1 and 2, Efficiency vs Load

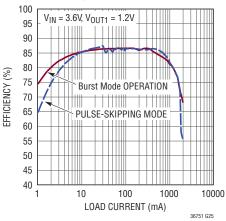

Boost Regulator, Efficiency vs Load

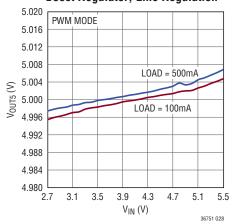

#### **Boost Regulator, Load Regulation**

#### TYPICAL PERFORMANCE CHARACTERISTICS

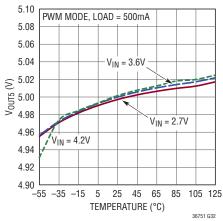

#### **Boost Regulator, Line Regulation**

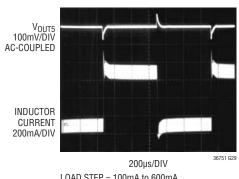

#### Boost Regulator Transient Response (PWM Mode)

LOAD STEP = 100mA to 600mA  $V_{IN} = 3.6$ V,  $V_{OUT5} = 5$ V

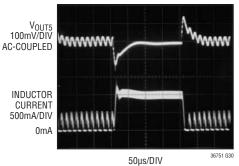

#### Boost Regulator Transient Response (Burst Mode Operation)

LOAD STEP = 100mA to 600mA V<sub>IN</sub> = 3.6V, V<sub>OUT5</sub> = 5V

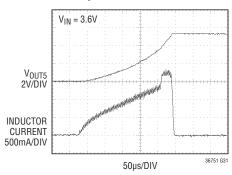

#### Boost Regulator, No Load Start-Up Transient, PWM Mode

#### Boost Regulator, V<sub>OUT5</sub> vs Temperature

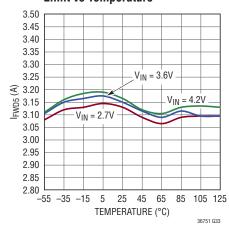

#### Boost Regulator, Forward Current Limit vs Temperature

#### TYPICAL PERFORMANCE CHARACTERISTICS

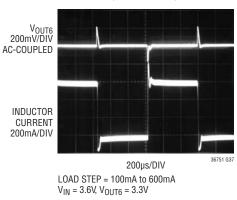

#### Buck-Boost Regulator Transient Response (PWM Mode)

LOAD CURRENT (mA)

36751 G35

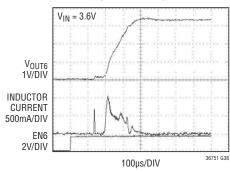

#### Buck-Boost Regulator No Load Start-Up (PWM Mode)

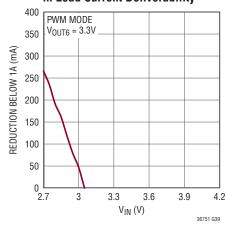

## Buck-Boost Regulator, Reduction in Load Current Deliverability

LINEAR TECHNOLOGY

#### TYPICAL PERFORMANCE CHARACTERISTICS

## Buck-Boost Regulator, V<sub>OUT6</sub> vs Temperature

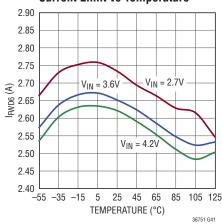

#### Buck-Boost Regulator, Forward Current Limit vs Temperature

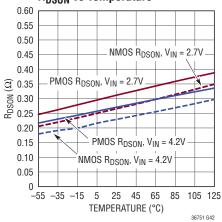

## Buck-Boost Regulator, Switch R<sub>DSON</sub> vs Temperature

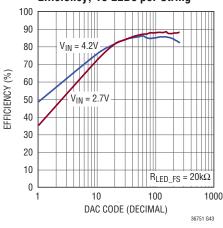

LED Driver, Dual String Efficiency, 10 LEDs per String

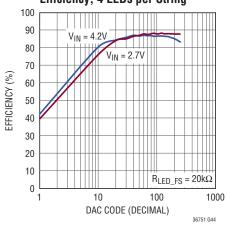

LED Driver, Dual String Efficiency, 4 LEDs per String

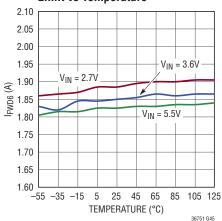

LED Driver, Forward Current Limit vs Temperature

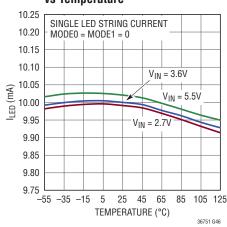

LED Driver, LED Current vs Temperature

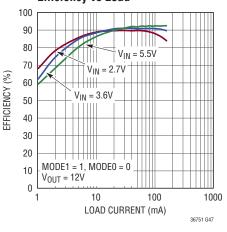

High Voltage Boost Regulator, Efficiency vs Load

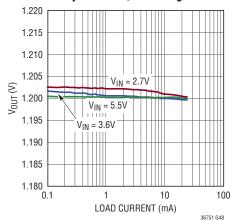

Always-On LDO, Load Regulation

#### PIN FUNCTIONS

**EN1 (Pin 1):** Buck Regulator 1 Enable Input. Active high. This pin is a high impedance input; do not float.

**FB1 (Pin 2):** Buck Regulator 1 Feedback Pin. Receives feedback by a resistor divider connected across the output.

**FB2** (**Pin 3**): Buck Regulator 2 Feedback Pin. Receives feedback by a resistor divider connected across the output. Connecting FB2 to  $V_{\text{IN}}$  combines buck regulator 2 with buck regulator 1 for higher current.

**EN2 (Pin 4):** Buck Regulator 2 Enable Input. Active high. This pin is a high impedance input; do not float.

**SW1 (Pin 5):** Buck Regulator 1 Switch Node. External inductor connects to this pin.

$V_{IN}$  (Pin 6): Buck Regulator 1 Input Supply. A  $10\mu$ F decoupling capacitor to GND is recommended. Must be connected to all other  $V_{IN}$  supply pins (Pins 7, 10, 31, 34, 40).

$V_{IN}$  (Pin 7): Buck Regulator 2 Input Supply. A  $10\mu$ F decoupling capacitor to GND is recommended. Must be connected to all other  $V_{IN}$  supply pins (Pins 6, 10, 31, 34, 40).

**SW2 (Pin 8):** Buck Regulator 2 Switch Node. External inductor connects to this pin.

**SW3 (Pin 9):** Buck Regulator 3 Switch Node. External inductor connects to this pin.

$V_{IN}$  (Pin 10): Buck Regulators 3 and 4 Input Supply. A  $10\mu\text{F}$  decoupling capacitor to GND is recommended. Must be connected to all other  $V_{IN}$  supply pins (Pins 6, 7, 31, 34, 40).

**SW4 (Pin 11):** Buck Regulator 4 Switch Node. External inductor connects to this pin.

**EN3 (Pin 12):** Buck Regulator 3 Enable Input. Active high. This pin is a high impedance input; do not float.

**EN4 (Pin 13):** Buck Regulator 4 Enable Input. Active high. This pin is a high impedance input; do not float.

**FB4 (Pin 14):** Buck Regulator 4 Feedback Pin. Receives feedback by a resistor divider connected across the output. Connecting FB4 to  $V_{IN}$  combines buck regulator 4 with buck regulator 3 for higher current.

**FB3 (Pin 15):** Buck Regulator 3 Feedback Pin. Receives feedback by a resistor divider connected across the output. Connecting FB3 to  $V_{\text{IN}}$  combines buck regulator 3 with buck regulator 2 for higher current.

**LED\_OV** (Pin 16): Overvoltage Protection Pin for LED Driver.

**LED1 (Pin 17):** Connect a string of up to 10 LEDs to this pin.

**SW7 (Pins 18, 19, 20):** LED Driver Switch Node. External inductor connects to these pins.

**LED2 (Pin 21):** Connect a string of up to 10 LEDs to this pin.

**CT (Pin 22):** Timing Capacitor Pin. A capacitor connected to GND sets a time constant which is scaled for use by the WAKE, RSTB and IRQB pins.

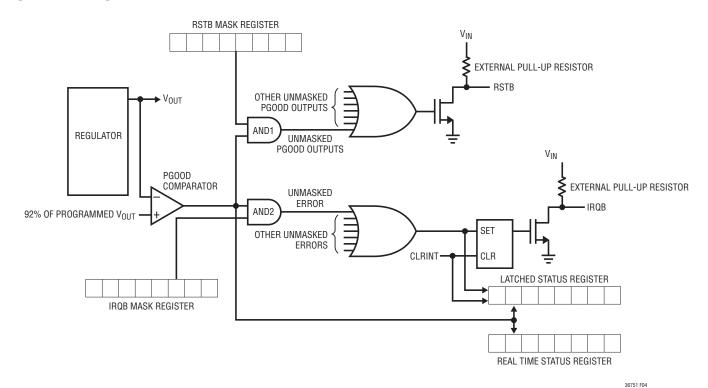

**RSTB** (**Pin 23**): Reset Pin. Open drain output. When the regulated output voltage of any enabled switching regulator is more than 8% below its programmed level, this pin is driven LOW. Assertion delay is scaled by the  $C_T$  capacitor.

**IRQB (Pin 24):** Interrupt Pin. Open drain output. When undervoltage, overtemperature, or an unmasked error condition is detected, this pin is driven LOW.

**PBSTAT (Pin 25):** Pushbutton Status Pin. Open drain output. This pin provides a debounced and glitch free status of the ONB pin.

#### PIN FUNCTIONS

**WAKE (Pin 26):** Open Drain Output. When the ONB pin is pressed and released, the signal is debounced and the WAKE signal is held HIGH for a minimum time period that is scaled by the  $C_T$  capacitor.

**LED\_FS (Pin 27):** A resistor connected from this pin to GND programs full-scale LED current.

ONB (Pin 28): Pushbutton Input. Active low.

**LDOFB** (Pin 29): LDO Feedback Pin. A resistor divider from LDO\_OUT to GND provides feedback.

**LDO\_OUT (Pin 30):** Output of Always-On LDO. Decouple with a 10µF capacitor to GND.

$V_{IN}$  (Pin 31): Quiet Input Supply Used to Power Non-Switching Control Circuitry. A 2.2 $\mu$ F decoupling capacitor to GND is recommended. Must be connected to all other  $V_{IN}$  supply pins (Pins 6, 7, 10, 34, 40).

**SW5 (Pin 32):** Boost Regulator Switch Node. External inductor connects to this pin.

**V<sub>OUT5</sub>** (**Pin 33**): Boost Regulator Output. Connect two 22µF capacitors to GND.

$V_{IN}$  (Pin 34): Quiet Input Supply Used to Power Non-Switching Control Circuitry. A 2.2µF decoupling capacitor to GND is recommended. Must be connected to all other  $V_{IN}$  supply pins (Pins 6, 7, 10, 31, 40).

**FB5 (Pin 35):** Boost Regulator Feedback Pin. Receives feedback by a resistor divider connected across the output.

**FB6 (Pin 36):** Buck-Boost Regulator Feedback Pin. Receives feedback by a resistor divider connected across the output.

**ENBB (Pin 37):** Buck-Boost Regulator Enable Input. Active high. This pin is a high impedance input; do not float.

**SWAB6 (Pin 38):** Buck-Boost Regulator Switch Pin. External inductor connects to this pin and SWCD6.

SCL (Pin 39): Clock Line for I<sup>2</sup>C Port.

$V_{IN}$  (Pin 40): Buck-Boost Regulator Input Supply. A 10 $\mu$ F decoupling capacitor to GND is recommended. Must be connected to all other  $V_{IN}$  supply pins (Pins 6, 7, 10, 31, 34).

**DV<sub>CC</sub> (Pin 41):** Supply Pin for I<sup>2</sup>C Port.

$V_{OUT6}$  (Pins 42): Buck-Boost Regulator Output. Connect a  $22\mu F$  capacitor to GND.

**SDA (Pin 43):** Serial Data Line for I<sup>2</sup>C Port. Open drain output during readback.

**SWCD6 (Pin 44):** Buck-Boost Regulator Switch Pin. External inductor connects to this pin and SWAB6.

**GND (Exposed Pad Pin 45):** Ground for Entire Chip. Must be soldered to PCB for electrical contact and rated thermal performance.

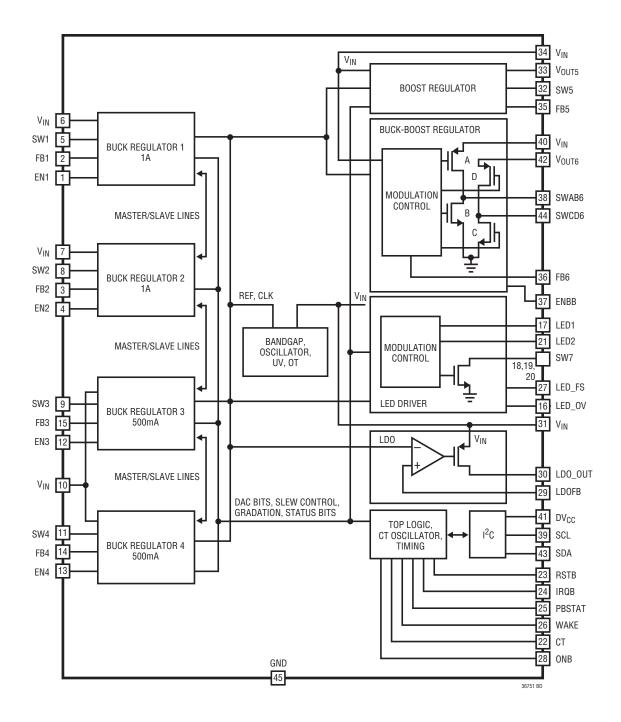

#### **BLOCK DIAGRAM**

The LTC3675/LTC3675-1 have six monolithic synchronous switching regulators and a dual string boost LED driver and is designed to operate from a single Li-Ion battery. All of the switching regulators and the LED driver are internally compensated and need only external feedback resistors for regulation. The switching regulators also offer two operating modes: Burst Mode operation for higher efficiency at light loads and pulse-skipping/PWM mode. In Burst Mode operation at light loads, the output capacitor is charged to a voltage slightly higher than its regulation point. The regulator then goes into sleep, during which the output capacitor provides the load current. In sleep most of the regulator's circuitry is powered down, helping conserve battery power. When the output capacitor droops below its programmed value, the circuitry is powered on and another burst cycle begins. The sleep time decreases as load current increases.

All switching regulators and LED driver may be configured via I<sup>2</sup>C, providing the user with the flexibility to operate the LTC3675/LTC3675-1 in the most efficient manner. I<sup>2</sup>C commands can also be read back via the I<sup>2</sup>C port, to ensure a command was not corrupted during a transmission.

All the regulators can be enabled via I<sup>2</sup>C commands. The buck regulators and the buck-boost regulator may also be enabled via enable pins. The enable pins have two different enable threshold voltages that depend on the operating state of the LTC3675/LTC3675-1. With all regulators disabled, the enable pin threshold is at 650mV. If any regulator is enabled either by its enable pin or an I<sup>2</sup>C command, then the enable pin thresholds are at 400mV. A precision comparator detects a voltage greater than 400mV on the enable pin and turns that regulator on. This precision threshold may be used to sequentially enable regulators. If all regulators are disabled, all the command registers are set in their default state.

There are also 2 bytes of data that report any fault conditions on the LTC3675/LTC3675-1 via I<sup>2</sup>C read back.

#### **BUCK SWITCHING REGULATOR**

The LTC3675/LTC3675-1 contain four buck regulators. Two of the buck regulators are designed to deliver up to 1A load current each while the other two regulators can deliver up to 500mA each.

The buck regulators can operate in either of two modes. In pulse-skipping mode, the regulator will skip pulses at light loads but will operate at a constant frequency of 2.25MHz at higher loads. In Burst Mode operation, the regulator will burst at light loads whereas at higher loads it will operate at constant frequency PWM mode of operation, much the same as pulse-skipping mode at high load. In shutdown, an I<sup>2</sup>C control bit provides the flexibility to either keep the SW node in a high impedance state or pull the SW node to GND through a 10k resistor.

The buck regulators have forward and reverse current limiting, soft-start to limit inrush current during start-up, short-circuit protection and slew rate control for lower radiated EMI.

Each buck regulator may be enabled via its enable pin or I<sup>2</sup>C. The mode of operation, the feedback regulation voltage and switch slew rate can all be controlled via I<sup>2</sup>C. For applications that require higher power, buck regulators may be combined together.

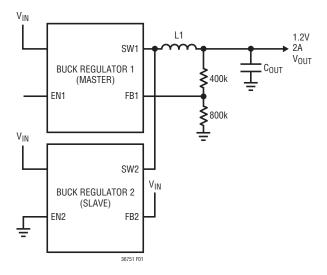

#### **BUCK REGULATORS WITH COMBINED POWER STAGES**

Two adjacent buck regulators may be combined in a master-slave configuration by connecting their SW pins together and connecting the higher numbered buck's FB pin to the input supply. The lower numbered buck is always the master. The higher numbered buck is a slave and its enable pin must be tied to ground. In Figure 1, buck

Figure 1. Buck Regulators Configured as Master-Slave

regulator 1 is the master. The feedback network connected to the FB1 pin programs the output voltage to 1.2V. The FB2 pin is tied to  $V_{\rm IN}$ , which configures buck regulator 2 as the slave. The SW1 and SW2 pins must be tied together. The register contents of the master program the combined buck regulator's behavior and the register contents of the slave are ignored. The slave buck control circuitry draws no current. The enable of the master buck (EN1) controls the operation of the combined bucks.

Buck regulators 2 and 3 may be configured as combined buck regulators capable of delivering up to 1.5A load current with buck regulator 2 being the master. Buck regulators 3 and 4 may be configured as combined buck regulators capable of delivering up to 1A load current with buck regulator 3 being the master.

#### **BOOST SWITCHING REGULATOR**

The boost regulator is capable of delivering up to 1A load current for a programmed output voltage of up to 5V. The boost regulator may be enabled only via I<sup>2</sup>C. The mode of operation, feedback regulation voltage and switch slew rate can all be controlled via I<sup>2</sup>C.

The boost regulator can operate in either PWM mode or in Burst Mode operation. In PWM operating mode, the regulator operates at a constant frequency of 2.25MHz and provides a low noise solution. For light loads, Burst Mode operation offers improved efficiency. The boost regulator has forward and reverse current limiting, soft-start to limit inrush current during start-up, short-circuit protection and slew rate control for lower radiated EMI. The boost regulator also features true output disconnect when in shutdown. In shutdown, an internal 10k resistor pulls the output to GND.

#### **BUCK-BOOST SWITCHING REGULATOR**

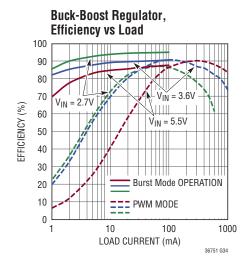

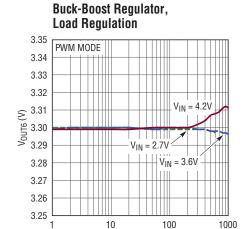

The buck-boost regulator is a 2.25MHz voltage mode regulator. The buck-boost regulator is capable of delivering up to 1A load current for a programmed output voltage of 3.3V. The regulator can be enabled via its enable pin or via I<sup>2</sup>C. The mode of operation, feedback regulation voltage and switch slew rate can all be controlled via I<sup>2</sup>C.

The buck-boost regulator can operate in either PWM mode or in Burst Mode operation. The PWM operating mode provides a low noise solution. For light loads, Burst Mode operation offers improved efficiency. The buck-boost regulator has forward current limiting, soft-start to limit inrush current during start-up, short-circuit protection and slew rate control for lower radiated EMI.

When the output voltage is below 2.65V (typical) during start-up, Burst Mode operation is disabled and switch D is turned off. The forward current is carried by the switch D well diode and there is no reverse current flowing in this condition. In shutdown, an internal 10k resistor pulls the output to GND.

#### **LED DRIVER**

The LED driver uses a constant frequency, current mode boost converter to supply power to up to two strings of 10 series LEDs. The series string of LEDs is connected from the output of the boost converter to an LED pin. The LED pin is a programmable constant current sink. The boost converter will regulate its output to force the LED pin to 300mV. The percentage of full-scale current sunk by the LED pin is programmed via 1<sup>2</sup>C.

The LED boost converter is designed for very high duty cycle operation and can boost from below 3V to 40V out at up to 55mA. The LED boost also features an overvoltage protection feature to limit the output voltage in case of an open circuit in an LED string. The boost converter will operate in either continuous conduction mode, discontinuous conduction mode or pulse-skipping mode depending on the inductor current required for regulation. The boost converter may also be configured to operate as an independent high voltage boost regulator via I<sup>2</sup>C. The LED driver may also be configured as a single string LED driver. When driving a single string, LED1 and LED2 should be tied together.

The LED driver features a fully automatic gradation circuit. This circuit allows the current to ramp up or down at a controlled rate between any two current levels. On power-up the LED DAC register is set to 0. To enable the LED driver a non-zero value must be programmed into this register.

LINEAR TECHNOLOGY

The gradation circuit will then ramp the current to the programmed value at a rate determined by the gradation rate bits. Once the LED driver reaches this value it will regulate that current until programmed otherwise. If a new value is programmed in the LED brightness register, the LED driver's current will ramp up or down at the programmed rate until that current is reached. To disable the LED driver, a code of zero is programmed in the LED DAC register. The gradation circuit will then ramp the current down at the programmed rate. Once the current reaches zero the gradation circuit will disable the boost and the entire LED driver will enter shutdown mode.

The LED driver is protected by the LED\_OV pin. This pin acts as a secondary feedback path that limits the voltage on the output capacitor. A feedback divider is placed from the LED boost's output to the LED\_OV pin. Values for this divider are selected to limit the output voltage similarly to the feedback dividers discussed in "Switching Regulator Output Voltage and Feedback Network" in the Applications Information section. The LED driver begins to transition to LED\_OV control at 800mV and is fully controlled by the LED\_OV pin by 825mV. During this transition the LED pins will begin to drop out of regulation. For this reason during normal operation the voltage on this pin should be kept below 800mV.

The LED driver is also designed to limit the maximum voltage on the LED1 and LED2 pins to no more than 8V. The boost regulates the minimum voltage on either LED pin. If one of the LED pins is shorted to ground the boost will only drive the other LED pin up to the voltage clamp, or the LED\_OV voltage, whichever is lower. If one LED string is shorted, or partially shorted, this clamp will prevent the boost from damaging the LED pin.

## PUSHBUTTON INTERFACE AND POWER-UP POWER-DOWN SEQUENCING

The LTC3675/LTC3675-1 provide pushbutton functionality to either power up or power down the part. The ONB, WAKE and PBSTAT pins provide the user with flexibility to power up or power down the part in addition to having I<sup>2</sup>C control. All PB timing parameters are scaled using

the CT pin. Times described below apply to a nominal  $C_T$  of  $0.01 \mu F$ .

The LTC3675/LTC3675-1 are in an off state when it is powered up with all regulators in shutdown. The WAKE pin is LOW in the off state. The WAKE pin will go HIGH either if ONB is pulled LOW for 400ms or a regulator is enabled via its enable pin or an I<sup>2</sup>C command. The WAKE pin stays in its HIGH state for 5 seconds and then gets pulled low. WAKE will not go HIGH again if a second regulator is subsequently enabled. The LTC3675/LTC3675-1 are in an on state if either the WAKE pin is HIGH or a regulator is enabled.

The PBSTAT pin reflects the status of the ONB when the LTC3675/LTC3675-1 are in an on state. Once in the on state, the LTC3675/LTC3675-1 can be powered down by holding ONB LOW for at least 5 seconds. All enabled regulators will be turned off for 1 second and the contents of the program registers are reset to their default state. This manner of power-down is called a hard reset. A hard reset may also be generated by using an I<sup>2</sup>C command.

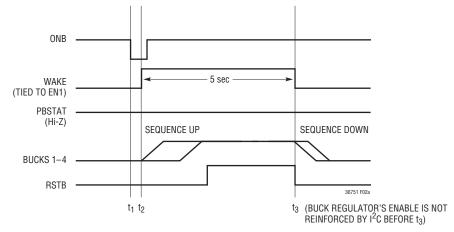

#### POWER-UP AND POWER-DOWN VIA PUSHBUTTON

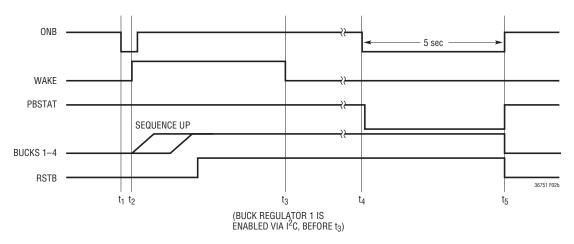

The LTC3675/LTC3675-1 may be turned on and off using the WAKE pin as shown in Figures 2a and 2b. In Figures 2a and 2b, pressing ONB low at time  $t_1$ , causes the WAKE pin to go high at time  $t_2$  and stay high for 5 seconds, after which WAKE is pulled low. WAKE going HIGH at  $t_2$  causes buck regulator 1 to power up, which sequentially powers up the other buck regulators. The RSTB pin gets pulled HIGH 200ms after the last enabled buck is in its PGOOD state. An application showing sequential regulator start-up is shown in the Typical Applications section (Figure 7).

If an  $I^2C$  command is written before the 5 second WAKE period  $t_3$  to keep the buck regulators enabled, the regulators stay enabled as shown in Figure 2b. Otherwise, when WAKE gets pulled low at  $t_3$ , the buck regulators will also power down sequentially as shown in Figure 2a.

In Figure 2b, ONB is held LOW at instant  $t_4$  for 5 seconds. This causes a hard reset to be generated and at  $t_5$ , all regulators are powered down.

Figure 2a. Power-Up Using WAKE (Sequenced Power-Up, Figure 7)

Figure 2b. Power-Up Using WAKE and Power-Down Due to Hard Reset (Sequenced Power-Up, Figure 7)

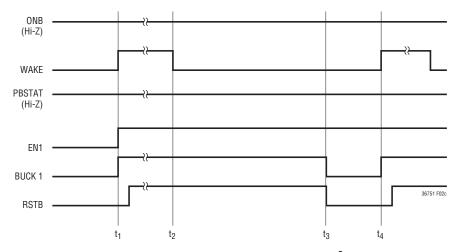

Figure 2c. Power-Up Using an Enable Pin and Power-Down Due to I<sup>2</sup>C Generated Hard Reset

#### POWER-UP AND POWER-DOWN VIA ENABLE PIN OR I<sup>2</sup>C

With the LTC3675/LTC3675-1 in its off state, a regulator can be enabled either via its enable pin or  $I^2C$ . In Figure 2c, buck regulator 1 is enabled via its enable pin at time  $t_1$ . The WAKE pin goes HIGH for 5 seconds and at  $t_2$  is pulled LOW. The buck regulator stays enabled until time  $t_3$  when a hard reset command is issued via  $I^2C$ . The buck regulator powers down and stays off for 1 second. At time  $t_4$ , the LTC3675/LTC3675-1 exit from the power down state. Since the buck regulator 1 is still enabled via its enable pin, it powers back up. WAKE also gets pulled HIGH for 5 seconds. The RSTB pin gets pulled HIGH 200ms after the buck regulator 1 is in its PGOOD state.

#### LED CURRENT PROGRAMMING

The LED current is primarily controlled through the LED DAC register at I<sup>2</sup>C sub-address 8. This register controls an 8 bit current DAC. A 20k resistor placed between the LED\_FS pin and ground provides a current reference for the DAC which results in 98µA of programmed LED current per LSB. For example, programming a LED DAC register code of 64h will result in a LED current of 9.8mA and a full-scale setting of FFh will result in a LED current of 25mA.

The 2xFS bit which is bit 3 of the LED configuration register at sub-address 7 effectively doubles the programmed LED current. With a 20k resistor from LED\_FS to ground each LSB will be 196µA. Programming a LED DAC register

code of 64h will result in a LED current of 19.6mA and a full-scale setting of FFh will result in an LED current of 50mA. The 2xFS mode is only intended for use when the output voltage is below 20V.

#### I<sup>2</sup>C INTERFACE

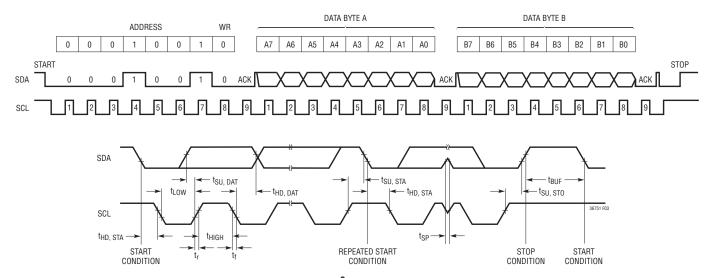

The LTC3675/LTC3675-1 may communicate with a bus master using the standard I $^2$ C 2-wire interface. The timing diagram (Figure 3) shows the relationship of the signals on the bus. The two bus lines, SDA and SCL, must be high when the bus is not in use. External pull-up resistors or current sources, such as the LTC1694 SMBus accelerator, are required on these lines. The LTC3675/LTC3675-1 are both a slave receiver and slave transmitter. The I $^2$ C control signals, SDA and SCL are scaled internally to the DV $_{CC}$  supply. DV $_{CC}$  should be connected to the same power supply as the bus pull-up resistors.

The  $I^2C$  port has an undervoltage lockout on the DV<sub>CC</sub> pin. When DV<sub>CC</sub> is below 1V, the  $I^2C$  serial port is cleared and the LTC3675/LTC3675-1 registers are set to their default configurations.

#### I<sup>2</sup>C Bus Speed

The I<sup>2</sup>C port is designed to be operated at speeds of up to 400kHz. It has built-in timing delays to ensure correct operation when addressed from an I<sup>2</sup>C compliant master device. It also contains input filters designed to suppress glitches should the bus become corrupted.

Figure 3. I<sup>2</sup>C Bus Operation

36751fd

#### I<sup>2</sup>C Start and Stop Conditions

A bus master signals the beginning of communications by transmitting a START condition. A START condition is generated by transitioning SDA from HIGH to LOW while SCL is HIGH. The master may transmit either the slave write or the slave read address. Once data is written to the LTC3675/LTC3675-1, the master may transmit a STOP condition which commands the LTC3675/LTC3675-1 to act upon its new command set. A STOP condition is sent by the master by transitioning SDA from LOW to HIGH while SCL is HIGH. The bus is then free for communication with another I<sup>2</sup>C device.

#### I<sup>2</sup>C Byte Format

Each byte sent to or received from the LTC3675/LTC3675-1 must be 8 bits long followed by an extra clock cycle for the acknowledge bit. The data should be sent to the LTC3675/LTC3675-1 most significant bit (MSB) first.

#### I<sup>2</sup>C Acknowledge

The acknowledge signal is used for handshaking between the master and the slave. When the LTC3675/LTC3675-1 are written to (write address), it acknowledges its write address as well as the subsequent two data bytes. When it is read from (read address), the LTC3675/LTC3675-1 acknowledge its read address only. The bus master should acknowledge receipt of information from the LTC3675/LTC3675-1.

An acknowledge (active LOW) generated by the LTC3675/LTC3675-1 lets the master know that the latest byte of information was received. The acknowledge related clock pulse is generated by the master. The master releases the SDA line (HIGH) during the acknowledge clock cycle. The LTC3675/LTC3675-1 pull down the SDA line during the write acknowledge clock pulse so that it is a stable LOW during the HIGH period of this clock pulse.

When the LTC3675/LTC3675-1 are read from, it releases the SDA line so that the master may acknowledge receipt of the data. Since the LTC3675/LTC3675-1 only transmit one byte of data during a read cycle, a master not acknowledging the data sent by the LTC3675/LTC3675-1 has no I<sup>2</sup>C specific consequence on the operation of the I<sup>2</sup>C port.

#### I<sup>2</sup>C Slave Address

The LTC3675 responds to a 7-bit address which has been factory programmed to b'0001001[R/WB]'. The LSB of the address byte, known as the read/write bit, should be 0 when writing data to the LTC3675 and 1 when reading data from it. Considering the address as an 8-bit word, the write address is 12h and the read address is 13h. The LTC3675-1 is factory programmed to b'0110100[R/WB]'. Its write address is 68h and the read address is 69h.

The LTC3675/LTC3675-1 will acknowledge both the read and write addresses.

#### I<sup>2</sup>C Sub-Addressed Writing

The LTC3675/LTC3675-1 have twelve command registers for control input. They are accessed by the I<sup>2</sup>C port via a sub-addressed writing system.

A single write cycle of the LTC3675/LTC3675-1 consists of exactly three bytes except when a clear interrupt command is written. The first byte is always the LTC3675/LTC3675-1's write address. The second byte represents the sub-address. The sub-address is a pointer which directs the subsequent data byte within the LTC3675/LTC3675-1. The third byte consists of the data to be written to the location pointed to by the sub-address. The LTC3675/LTC3675-1 contain 11 control registers which can be written to.

#### I<sup>2</sup>C Bus Write Operation

The master initiates communication with the LTC3675/LTC3675-1 with a START condition and the appropriate write address. If the address matches that of the LTC3675/LTC3675-1, the LTC3675/LTC3675-1 return an acknowledge. The master should then deliver the sub-address. Again the LTC3675/LTC3675-1 acknowledge and the cycle is repeated for the data byte. The data byte is transferred to an internal holding latch upon the return of its acknowledge by the LTC3675/LTC3675-1. This procedure must be repeated for each sub-address that requires new data. After one or more cycles of [ADDRESS][SUB-ADDRESS] [DATA], the master may terminate the communication with a STOP condition. Multiple sub addresses may be written to with a single address command using a

LINEAR TECHNOLOGY

Table 1. Summary of I<sup>2</sup>C Sub-Addresses and Byte Formats. Bits A7, A6, A5, A4 of Sub-Address Need to Be 0 to Access Registers

| SUB-ADDRESS<br>A7A6A5A4A3A2A1A0 | OPER-<br>ATION | ACTION                           | BYTE FORMAT<br>D7D6D5D4D3D2D1D0                                              | DEFAULT<br>D7D6D5D4D3D2D1D0 | COMMENTS                                                     |

|---------------------------------|----------------|----------------------------------|------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------|

| 0000 0000 (00h)                 | Write          | No Register<br>Selected          |                                                                              |                             | Used in the Clear Interrupt Operation.                       |

| 0000 0001 (01h)                 | Read/<br>Write | Buck1 Register                   | Enable, OUT_Hi-Z, Mode, Slow, DAC[3], DAC[2], DAC[1], DAC[0]                 | 01101111                    |                                                              |

| 0000 0010 (02h)                 | Read/<br>Write | Buck2 Register                   | Enable, OUT_Hi-Z, Mode, Slow, DAC[3], DAC[2], DAC[1], DAC[0]                 | 01101111                    |                                                              |

| 0000 0011 (03h)                 | Read/<br>Write | Buck3 Register                   | Enable, OUT_Hi-Z, Mode, Slow, DAC[3], DAC[2], DAC[1], DAC[0]                 | 01101111                    |                                                              |

| 0000 0100 (04h)                 | Read/<br>Write | Buck4 Register                   | Enable, OUT_Hi-Z, Mode, Slow, DAC[3], DAC[2], DAC[1], DAC[0]                 | 01101111                    |                                                              |

| 0000 0101 (05h)                 | Read/<br>Write | Boost Register                   | Enable, Unused, Mode, Slow, DAC[3], DAC[2], DAC[1], DAC[0]                   | 00001111                    |                                                              |

| 0000 0110 (06h)                 | Read/<br>Write | Buck-Boost<br>Register           | Enable, Unused, Mode, Slow, DAC[3], DAC[2], DAC[1], DAC[0]                   | 00001111                    |                                                              |

| 0000 0111 (07h)                 | Read/<br>Write | LED<br>Configuration<br>Register | Unused, Mode[1], Mode[0], Slow, 2XFS, GRAD[2], GRAD[1], GRAD[0]              | 00001111                    |                                                              |

| 0000 1000 (08h)                 | Read/<br>Write | LED DAC<br>Register              | DAC[7], DAC[6], DAC[5], DAC[4], DAC[3],<br>DAC[2], DAC[1], DAC[0]            | 00000000                    | 00000000 = LED Driver Disabled<br>11111111 = 25mA per String |

| 0000 1001 (09h)                 | Read/<br>Write | UVOT Register                    | RESET_ALL, UV[2], UV[1], UV[0], UNUSED, UNUSED, OT[1], OT[0]                 | 00000000                    |                                                              |